QuartusⅡ v13.1の使い方2~回路を作る編

ここでは、ALTERA社のQuartusⅡ v13.1の使い方についてご紹介します。同ツールを使えばVHDLやVerilogで記述した回路を論理合成したり、シミュレーションを行ったりすることで最終的にFPGA化することができます。今回紹介するバージョンは2024年8月時点において最新のバージョンではありませんが、シミュレーション時の入力パターンがグラフィカルに書けるなどのメリットがあるためQuartusⅡ v13.1をご紹介したいと思います。

回路を作る(言語入力する)

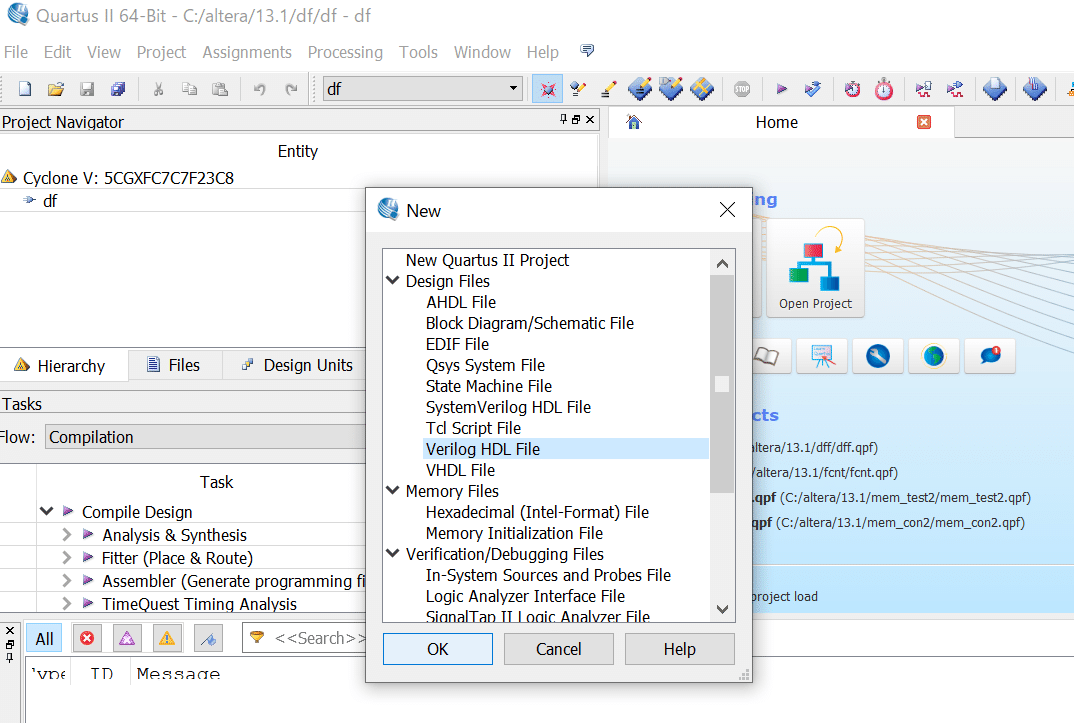

File->New->Verilog HDL File を選択してOKを押します。(今回はVerilogを例にして進めます)

右上にVerilog1.v タブが現れます。

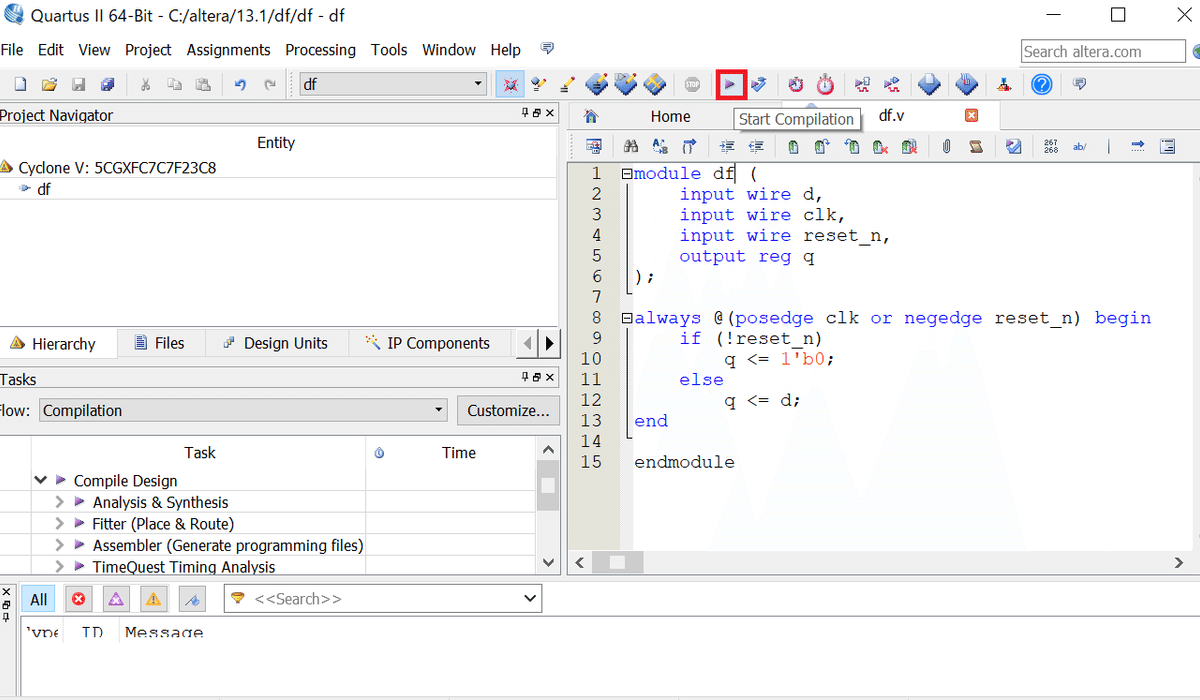

次に以下のように回路(言語)入力をします。今回はプロジェクト名をdffとしていますので例としてD型フリップフロップをイメージして記述します。(なお、必ずしもQuartusのエディタを使う必要はなく外部エディタで記述しても問題ありません)

コードは以下になりますのでコピペしてお使いください。

module df (

input wire d,

input wire clk,

input wire reset_n,

output reg q

);

always @(posedge clk or negedge reset_n) begin

if (!reset_n)

q <= 1'b0;

else

q <= d;

end

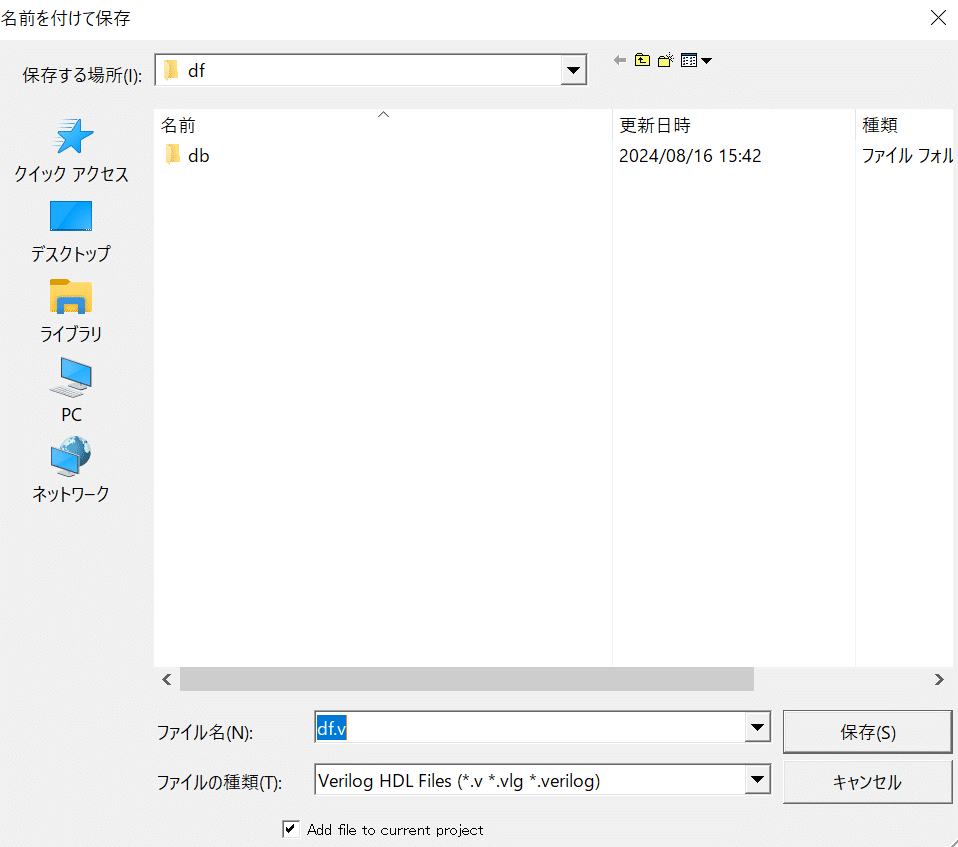

endmoduleファイルを保存します。File -> Save As… を選んでファイル名をdf.vとして保存します。(この時点で自動的にプロジェクト内にこのファイルが含まれるようになります)

次にコンパイル(論理合成等)をします。右上の赤枠部を押します。

PCの能力にもよりますが、おおむね1分程度で以下の画面(コンパイル終了)が出ます。

おわりに

ここでは回路入力~コンパイル(論理合成等)の一連の手順をご紹介しました。ありがとうございました。次はシミュレーションの一連の手順をご紹介します。

この記事が気に入ったらサポートをしてみませんか?