QuartusⅡ v13.1の使い方1~プロジェクトを作る編

ここでは、ALTERA社のQuartusⅡ v13.1の使い方についてご紹介します。同ツールを使えばVHDLやVerilogで記述した回路を論理合成したり、シミュレーションを行ったりすることで最終的にFPGA化することができます。今回紹介するバージョンは2024年8月時点において最新のバージョンではありませんが、シミュレーション時の入力パターンがグラフィカルに書けるなどのメリットがあるためQuartusⅡ v13.1をご紹介したいと思います。

まずはプロジェクトを作る

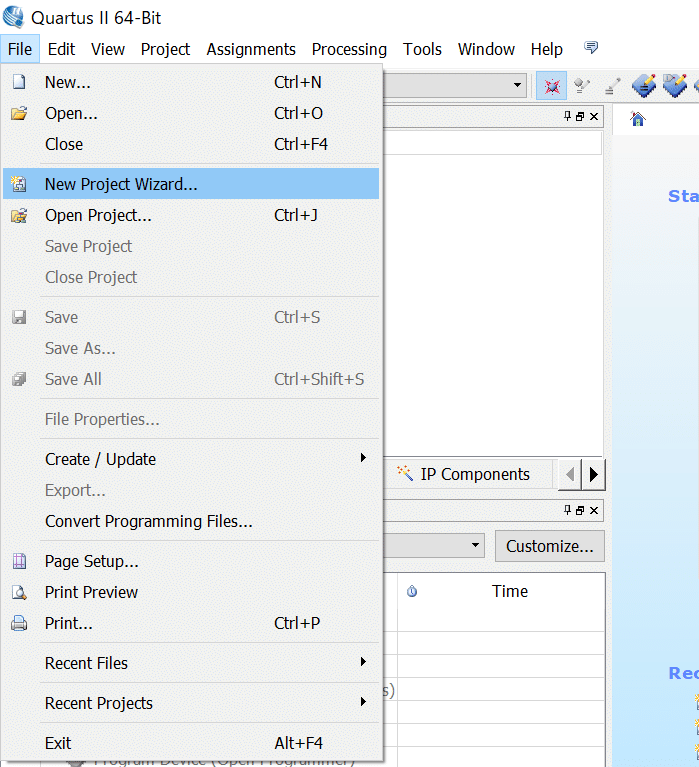

QuartusⅡ v13.1を起動したら、左上のFile-> New Project Wizard を選びます。

次に左下チェックボックスにチェックを入れてNextを押します。

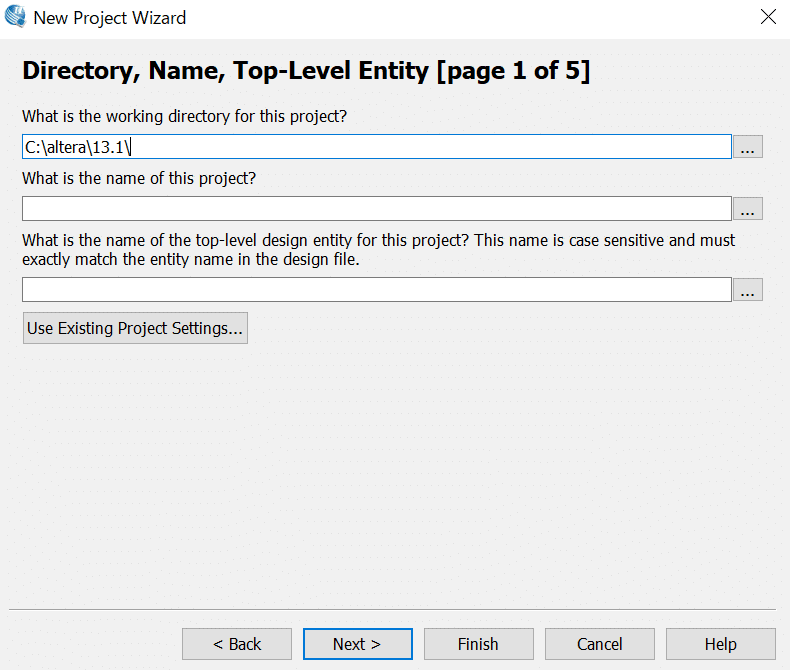

次に以下の画面が表示されます。

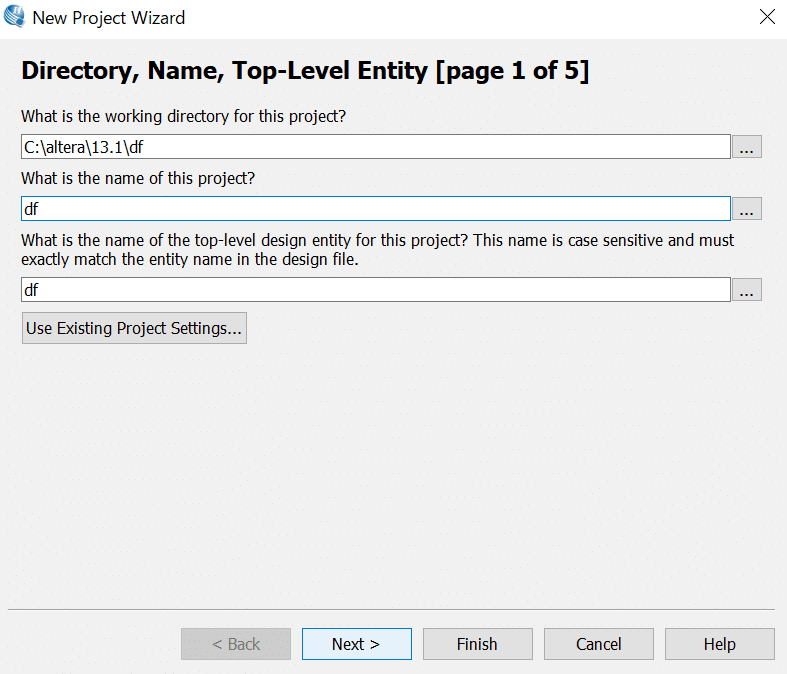

以下、これから作る回路のディレクトリやプロジェクト名などを入力していきます。ここではこれから作る回路名をdf(D型フリップフロップ)として下図のように入力します。(1行目~3行目にdfと入力する)入力が終わったらNextを押します。

以下、「指定されたディレクトリを新しく作って良いか?」と聞いてくるので Yes を押します。

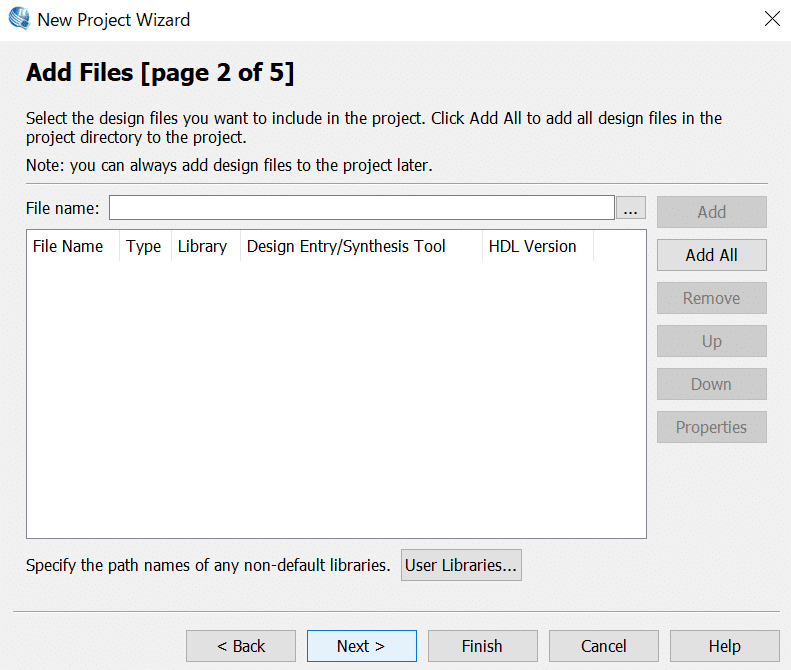

次に今回のプロジェクトに関係するファイルがあれば追加する指定を行う画面が出てきます。今回は最初にプロジェクトを作るためまだそのようなファイルはありませんので、何もAddすることなくNextを押します。

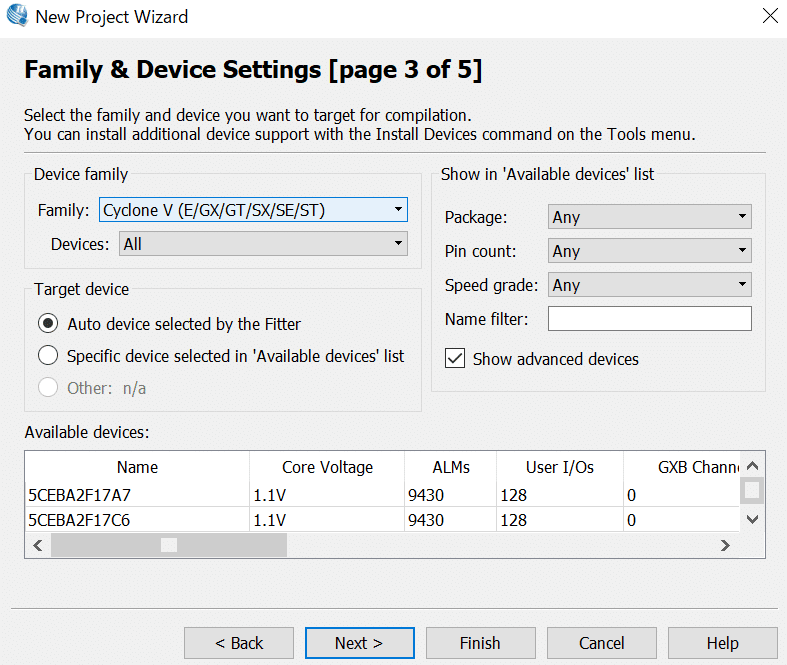

次に「どのFPGAを使うか」を指定するページが出ますが、何もせずNextを押すか、以下の様にFamilyのところを Cyclone V あたりを選んでNextを押します。

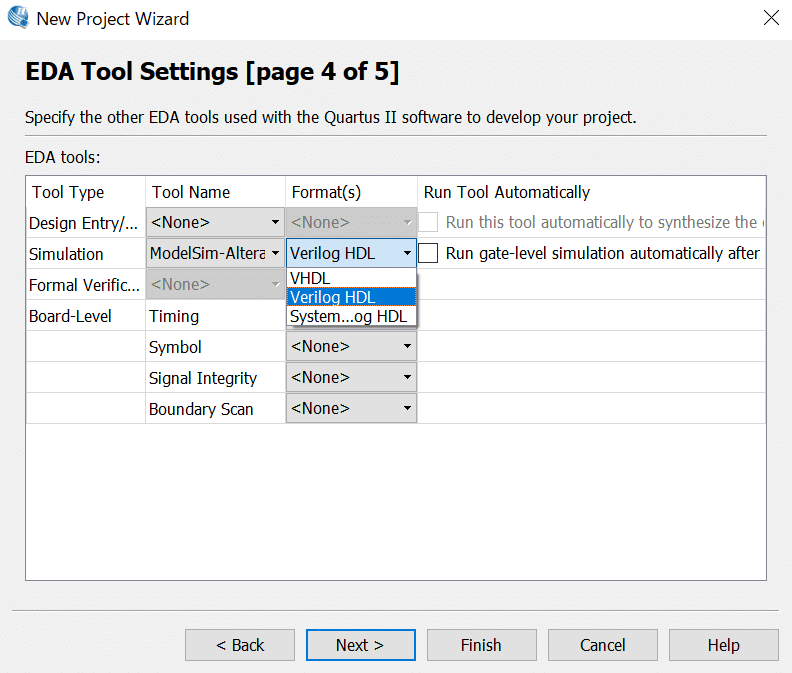

次にSimulation Format(s)のところで、使用言語を選択します。VHDLかVerilog HDLのどちらかを選択しますが、ここではVerilog HDLを選択します。選択したらNextを押します。

最後に今回設定したサマリが出ます。問題がなければFinishを押します。

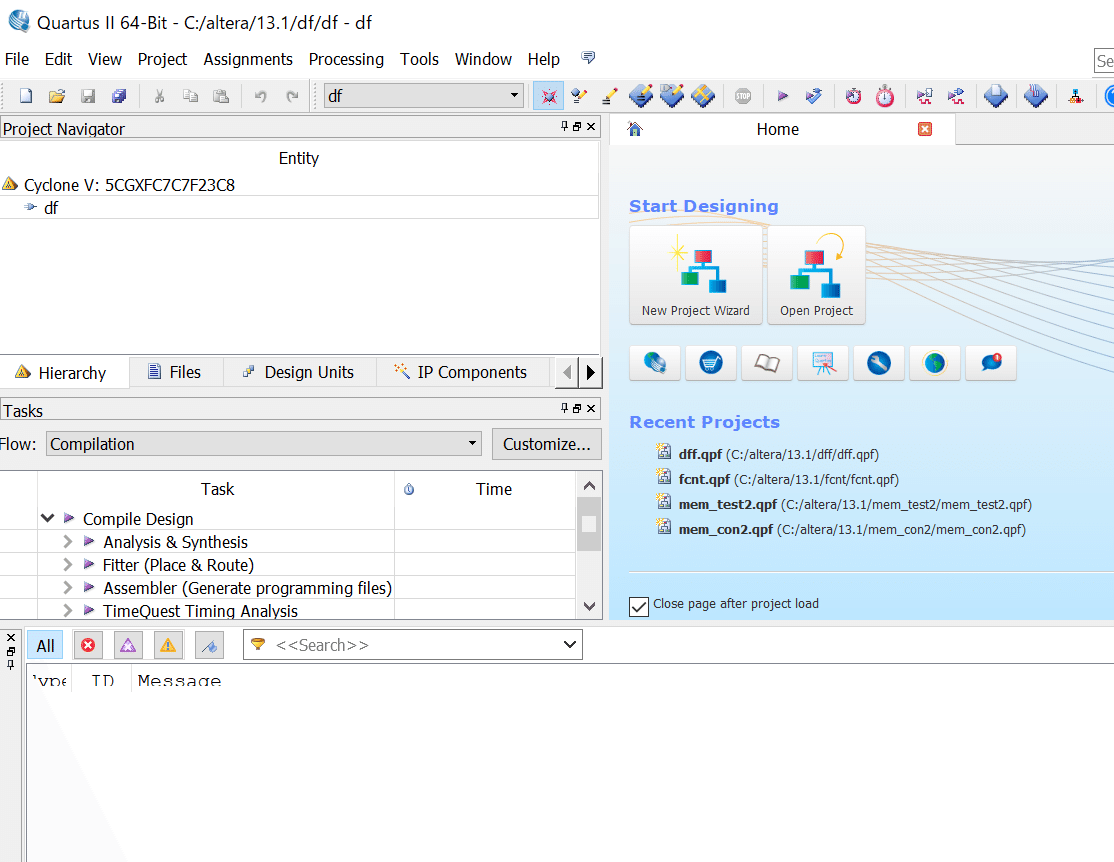

以下はプロジェクト作成が完了した画面になります。画面左上に、dfの記載があるかと思います。出ていれば問題ありません。

おわりに

回路を作る上で最初に行うことはプロジェクトを作ることになりますのでこの手順は覚えてください。ありがとうございました。次は実際に回路を入力する一連の手順をご紹介します。