QuartusⅡ v13.1の使い方3~シミュレーション編

ここでは、ALTERA社のQuartusⅡ v13.1の使い方についてご紹介します。同ツールを使えばVHDLやVerilogで記述した回路を論理合成したり、シミュレーションを行ったりすることで最終的にFPGA化することができます。今回紹介するバージョンは2024年8月時点において最新のバージョンではありませんが、シミュレーション時の入力パターンがグラフィカルに書けるなどのメリットがあるためQuartusⅡ v13.1をご紹介したいと思います。

テストパターンを作りシミュレーションを行う

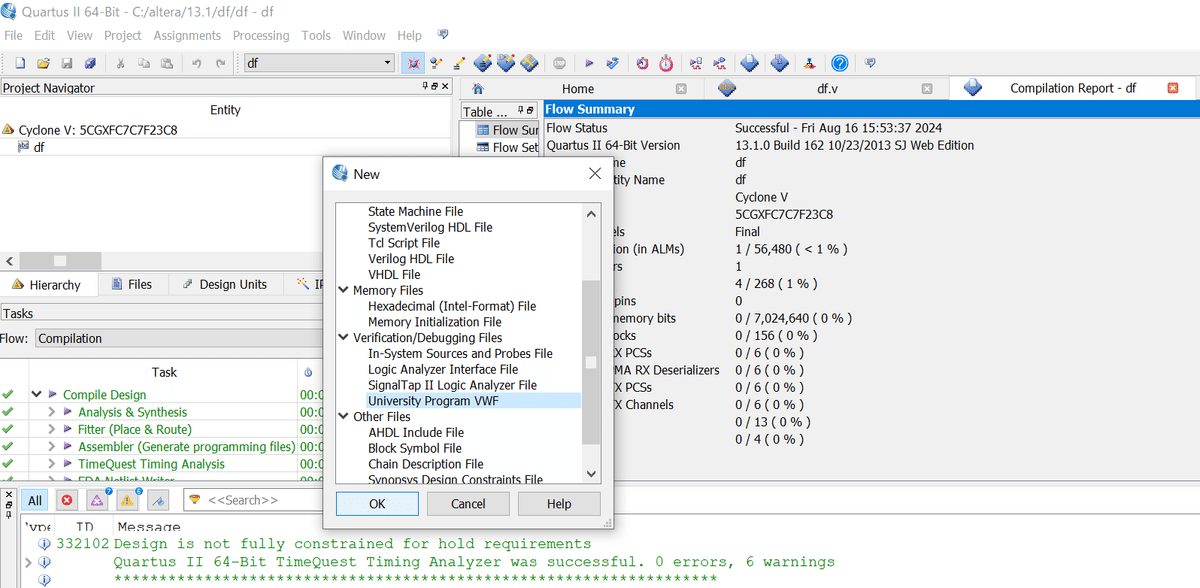

コンパイル(論理合成等)が終わったら、シミュレーションを行って作った回路が思い通りに動いているかどうかを確認します。まずFile -> New -> Verification/Debugging Files ->University Program VWF を選択してOKを押します。これでテストパターン(シミュレーション)を作る画面を呼び出します。

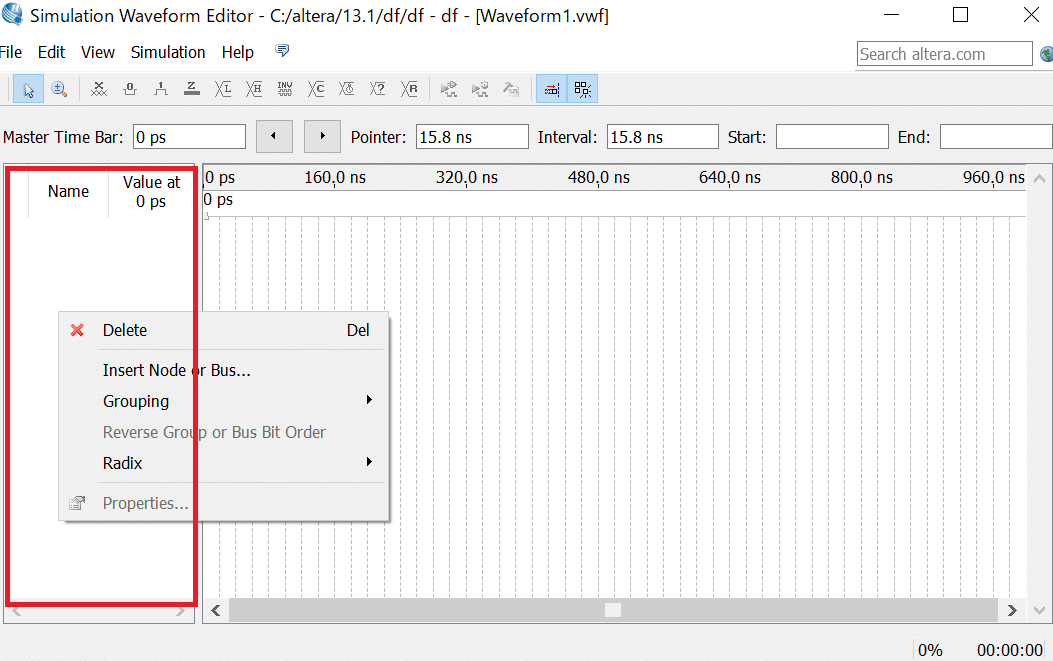

以下の画面が新たに表示されると思います。

次に赤枠内で右クリックし、以下の子画面を出します。

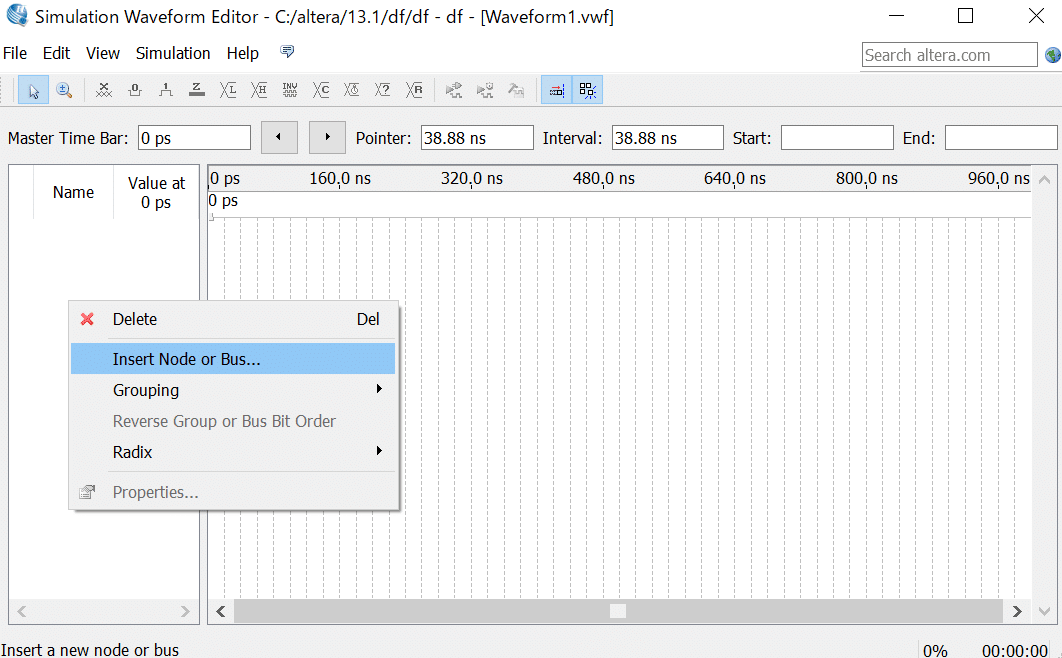

子画面の中でInsert Node or Bus… を選択します。

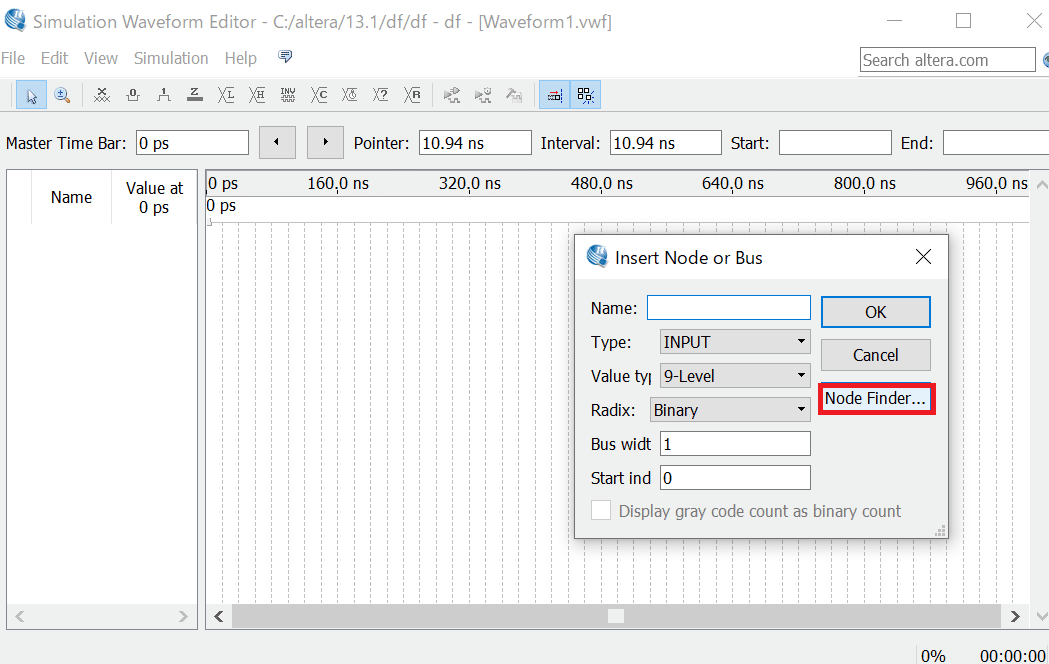

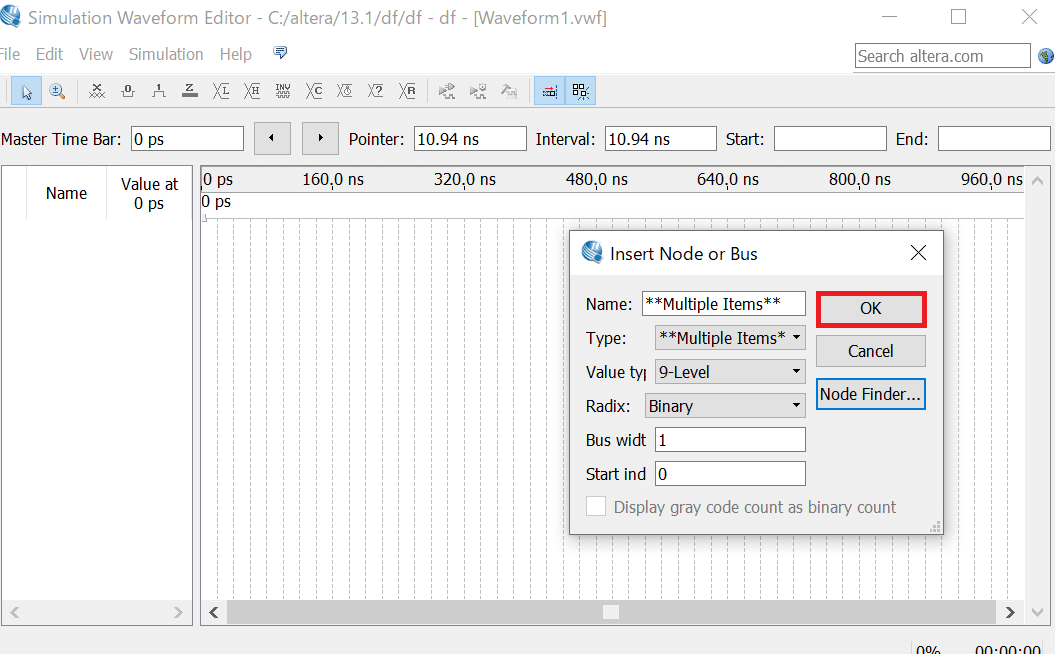

次に新に表示される子画面で Node Finder… を押します。

新たに以下の画面が表示されます。右上のListを押してください。

左側に今回の回路の入力、出力信号名が表示されたと思います。ここで中央の赤枠を押します。

以下の画面が出たら(右側に今回シミュレーションで使う信号群が出ている)右上のOKを押します。

以下の通り、子画面(Insert Node or Bus)中のOKを押します。

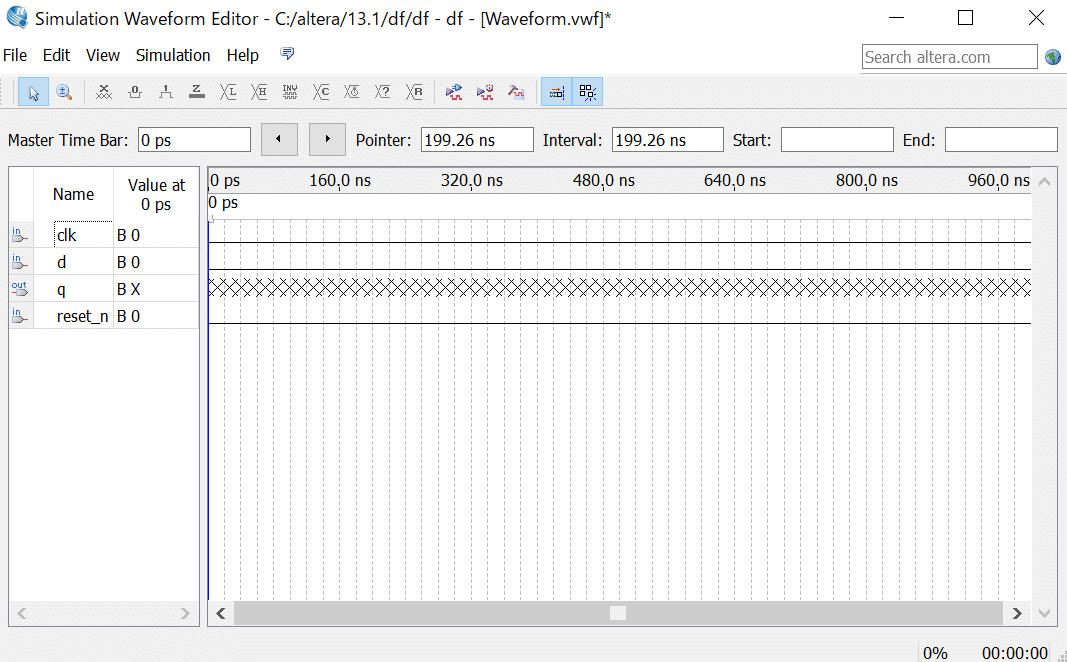

以下のテストパターン入力画面が表示されます。左側には信号名が入っていますね。

reset_nの信号名を左クリックしたまま、clkの上までドラッグして離します。(リセット信号を一番上にする場合)以下のような画面になります。

reset_n(リセット信号)をクリックし、

赤枠を押します。すると、reset_n信号がLからHへ切り替わります。

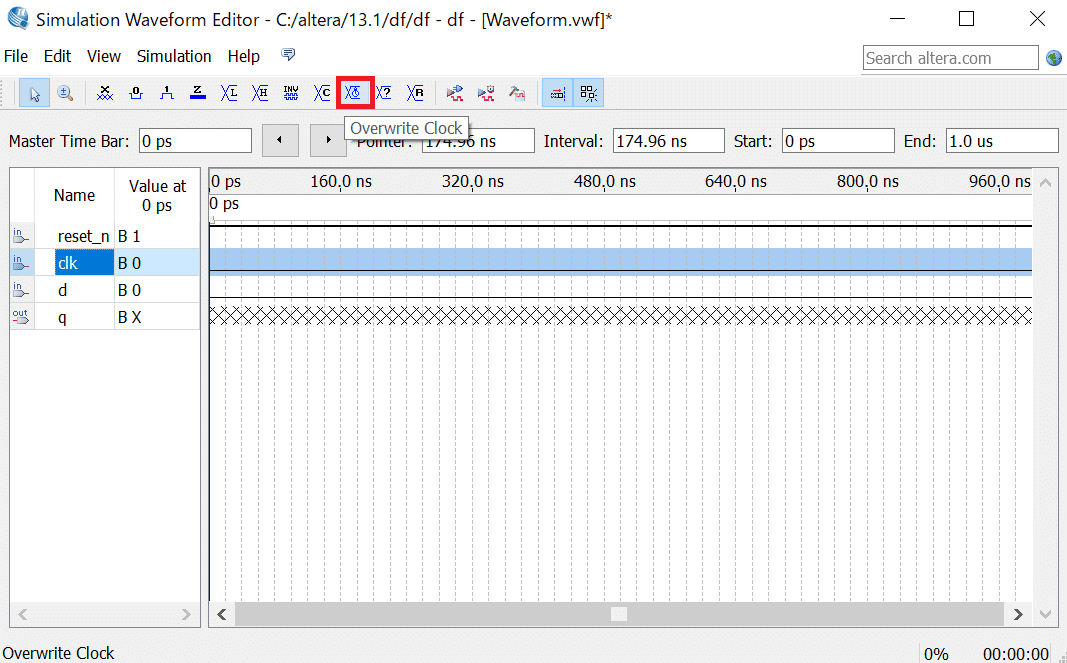

次に信号名clkをクリックし、赤枠の時計ボタンを押します。

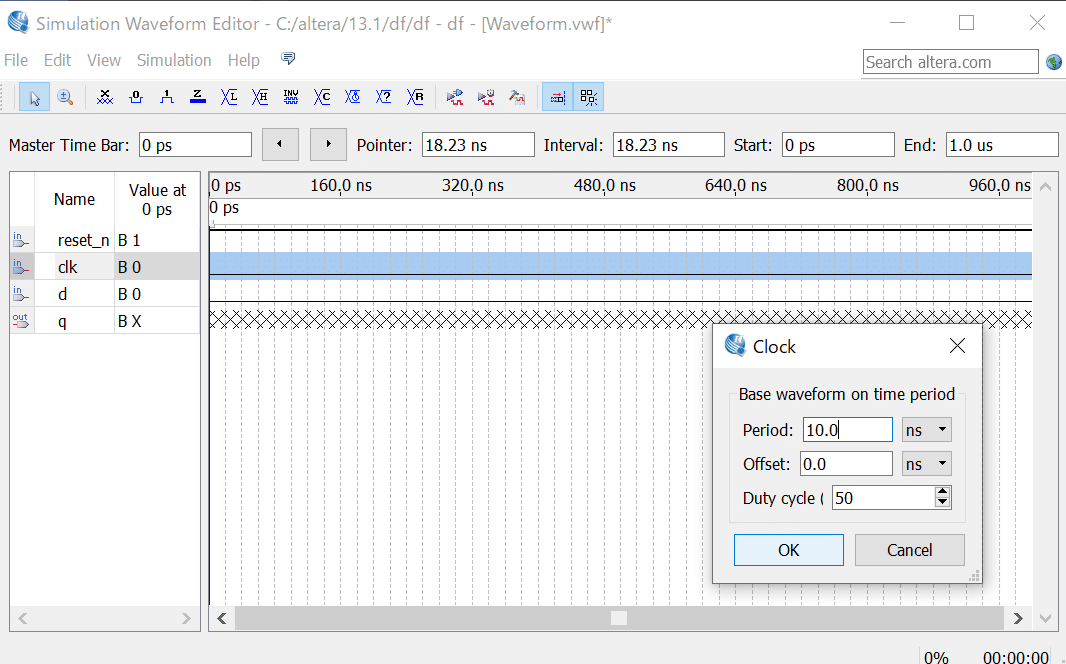

Clock の子画面が表示されたらOKを押します。

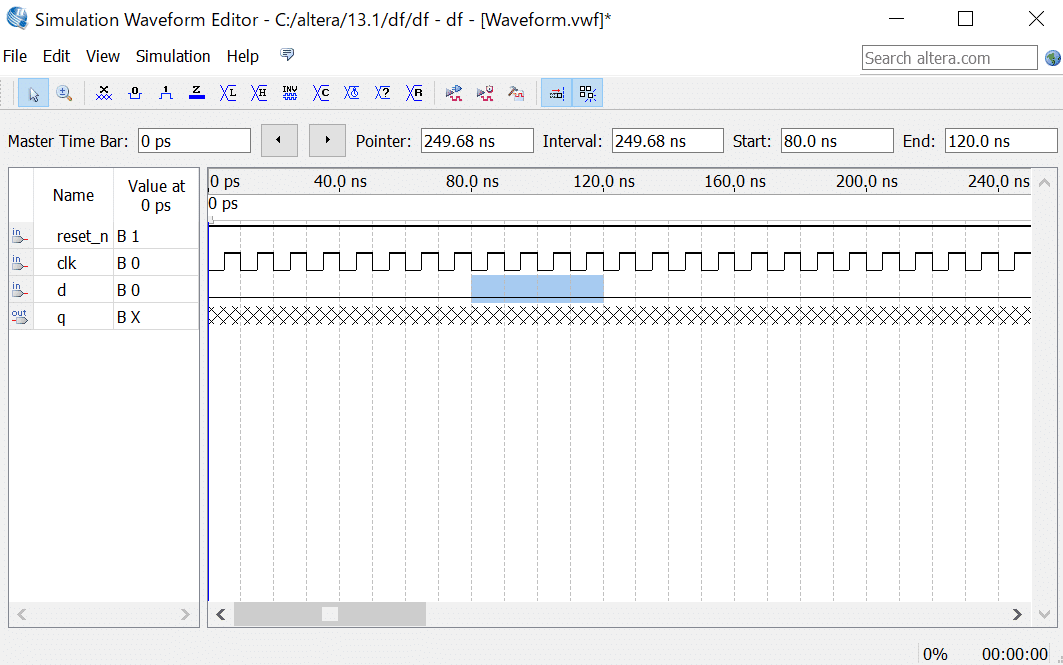

すると、以下の様にclkの信号が入っていることが確認できると思います。

次に、画面を拡大してみましょう。 View -> Zoom In で拡大することができます。

以下の通り拡大できました。

次にd信号の80ns~120nsを左クリックしながらドラッグします。(80nsで左クリックしながら120nsまでドラッグして離します。

赤枠の1を押すと、選択した領域がHレベルに変わります。

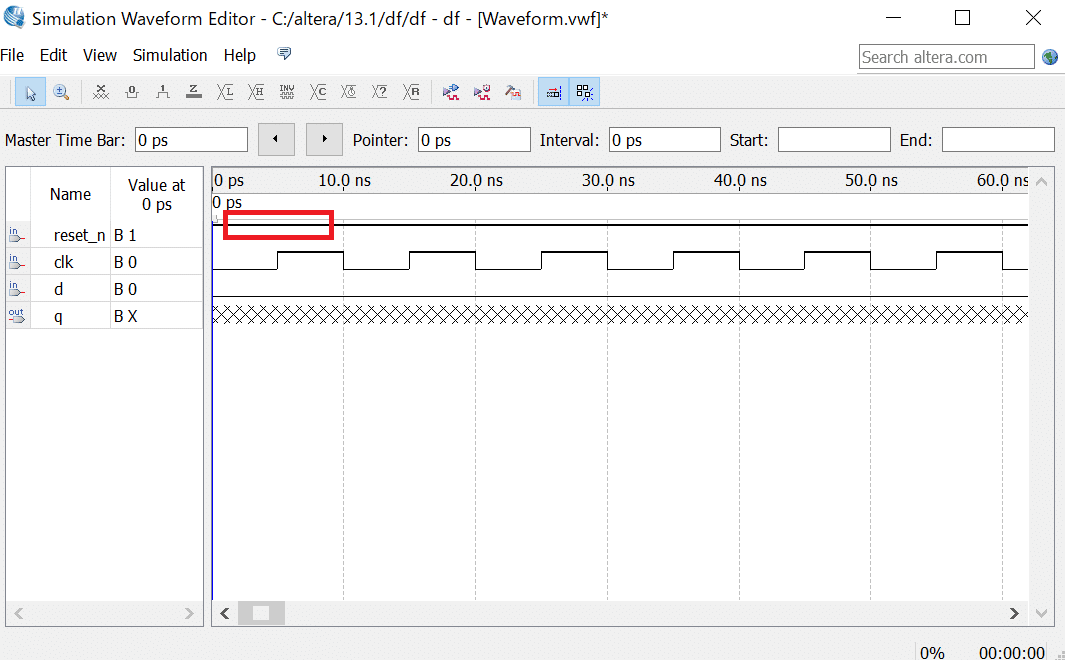

さらに View -> Zoom In で拡大します。

次にreset_nの0ps~10nsをLにするため、以下の赤枠を左クリック&ドラッグしてください。(ちょっと難しいかもしれませんが何回かチャレンジしてください)

以下の様になりました(選択された状態)でしょうか。

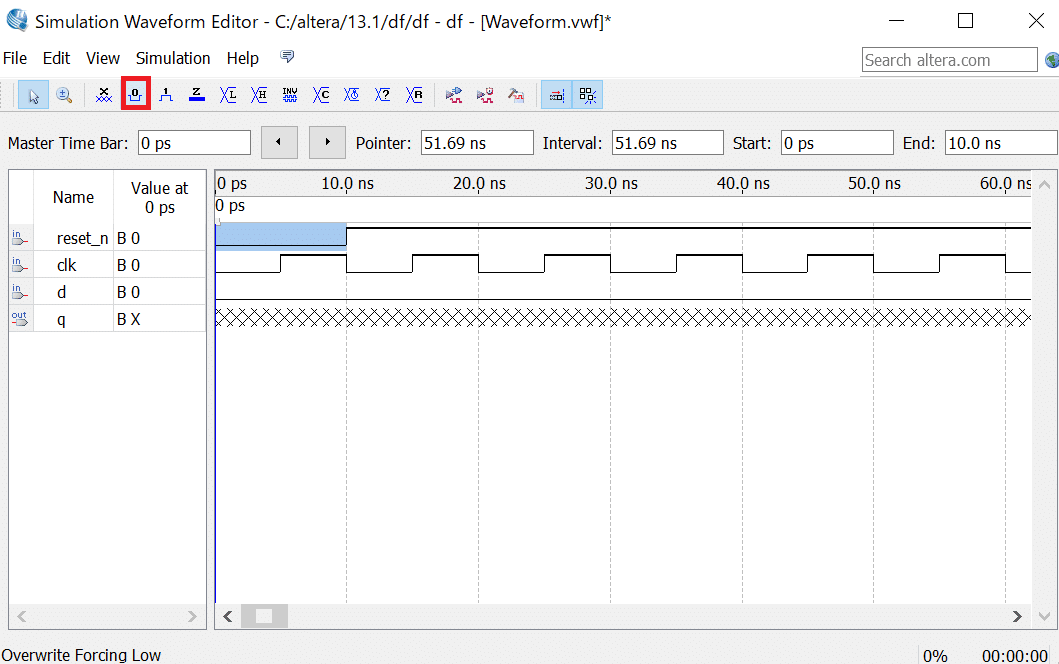

赤枠を押してreset_nをLレベルにしてください。これでついにテストパターンの入力が全てできました。お疲れ様です。

View->Zoom out で以下の様にします。(だいたいこれぐらいのレンジでd信号の立ち上がりと立下り付近が分かる程度)

作成したテストパターンを保存します。 File -> Save As …を選択します。

ファイル名はそのままにして保存を押します。

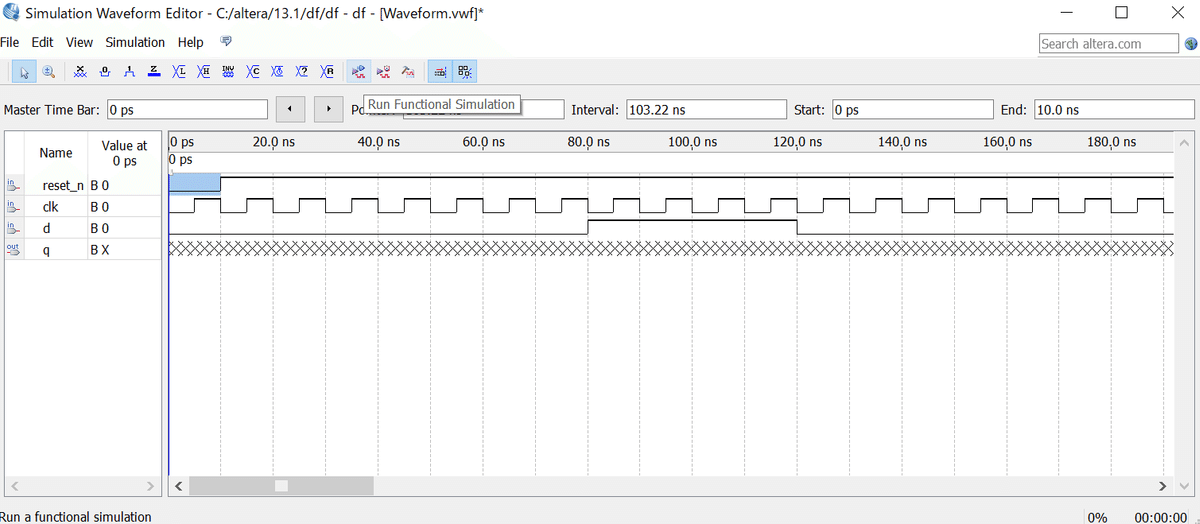

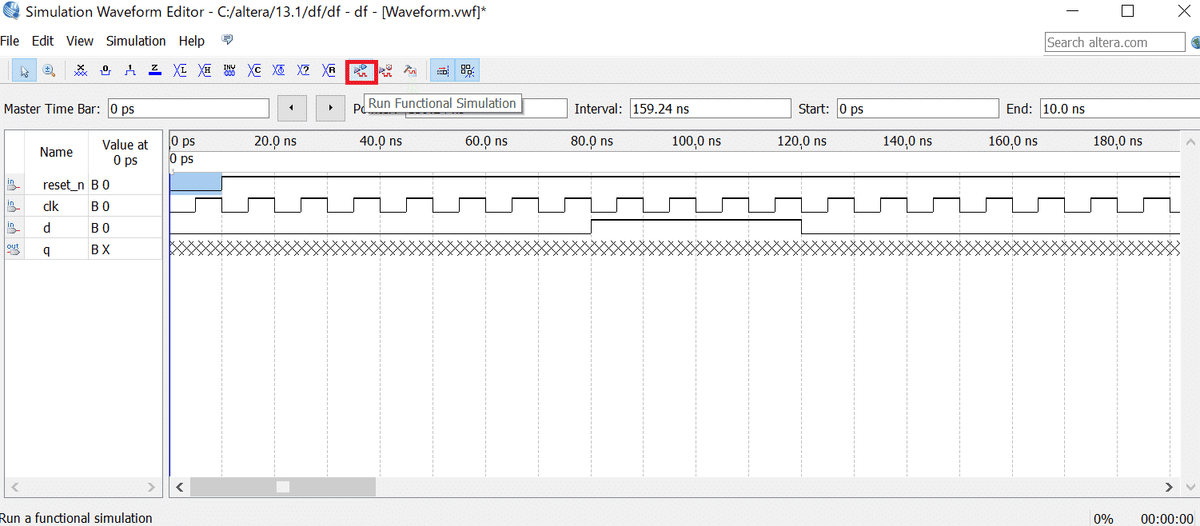

いよいよシミュレーションを開始します。赤枠を押します。

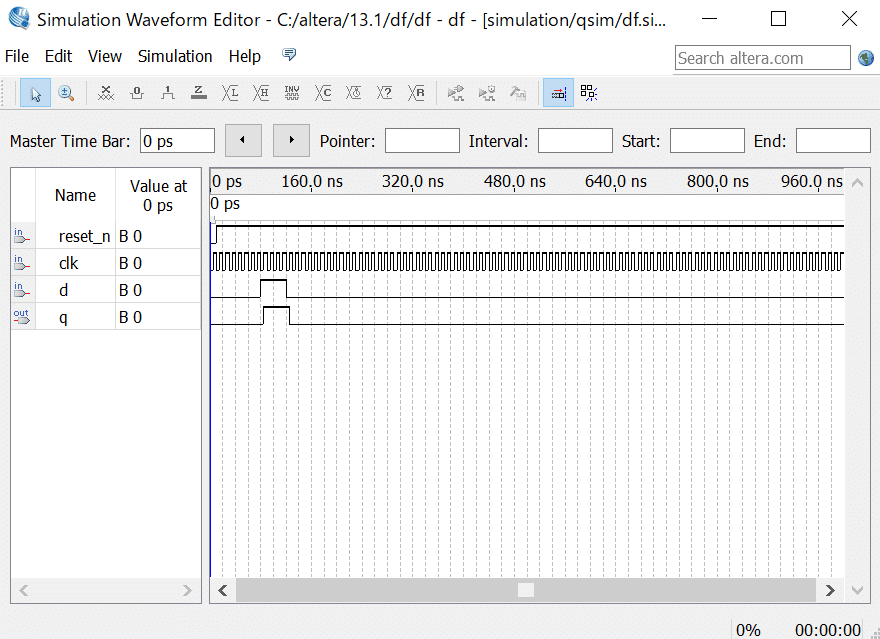

新たな画面(シミュレーション済)が表示されます。

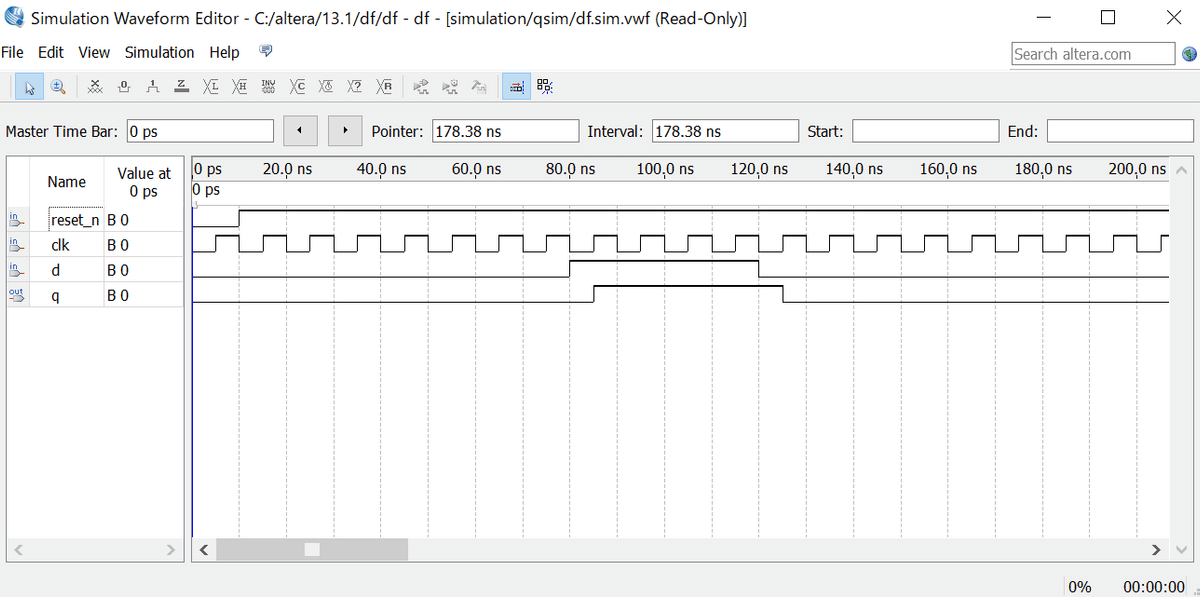

View -> Zoom In で以下の様に適度なレンジにします。

さあ、どうでしょう。

d信号の立ち上がりの後に来るclk信号の立ち上がりで出力qがHに遷移しています。また、d信号の立ち下がりの後に来るclk信号の立ち上がりで出力qがLに遷移しています。D型フリップフロップとして動作できていることが確認できました。

これでシミュレーションは終了です。なお、このシミュレーション結果はRead Onlyファイルとなっており保存することができません。(注意)

(再度シミュレーションをするときは、テストパターンの画面から再度シミュレーションを行ってください。)

おわりに

ここではシミュレーションの一連の手順をご紹介しました。最初は少し手間取るかもしれませんが、慣れてしまえば問題ないレベルだと思います。ありがとうございました。