NATUを作る(パート9)

HARUは失敗に終わってしまった。

だが、その悔しさをバネに、新たにNATUを作ることになった。

今回は、GRED IIのI/O関係を作っていきたいと思います。

制作

GRED IIは、演算結果をsushi memory architectureに出力します。

なので、VRAMとの橋渡しとなる回路が必要です。

では、実際に作っていきたいと思います!

気づいてしまった

そのために、まずは前回作った回路をコピーしましたが、ここである問題に気づきました。

なんと、レジスタの構造的に、一度に一か所しか情報を書き込めないようになっているのです!

想定では、一度にたくさんのレジスタに情報を書き込むことで、情報の伝達にかかる時間を短縮する想定でした。

なので、この構造ではいけません。

つまり、作り直しです。

まぁ、ちょうど間違えて4bitで十分なところ、8bitで作ってしまっていたので、この際についでに修正しちゃいましょう。

全て作り直し

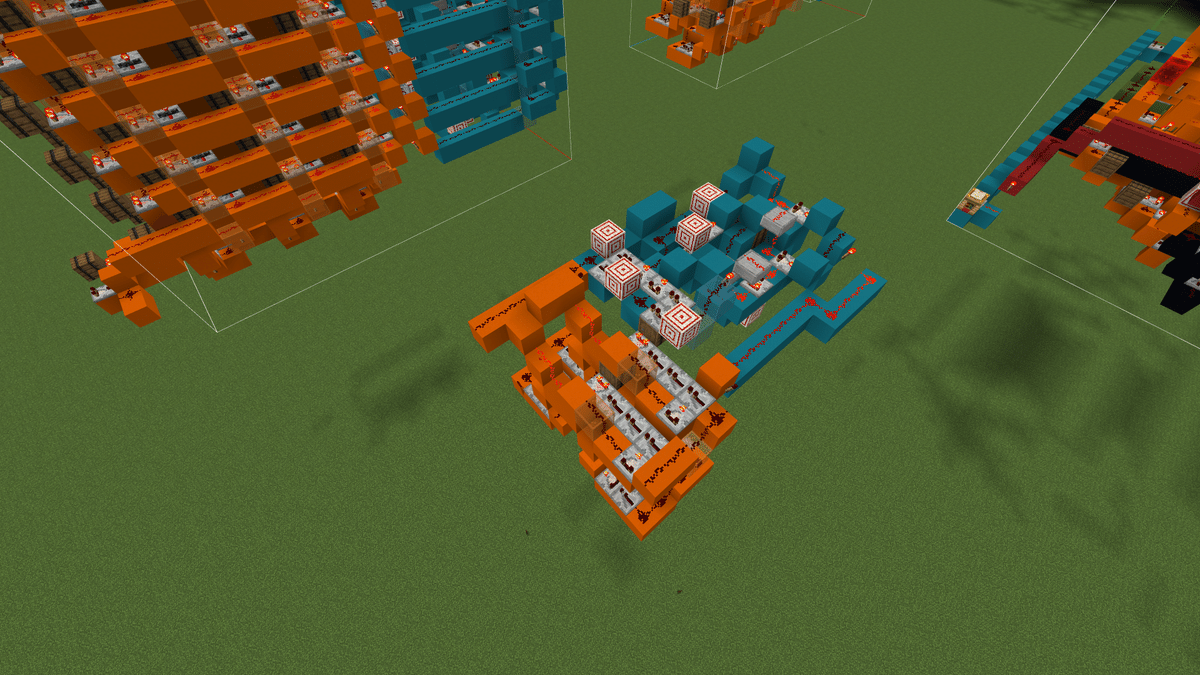

全て作り直しました。

ALUは、元々のやつをベースとしていて、4bit仕様にしています。

また、レジスタをデコーダーと一緒に変更したことで、幅を11から9に小型化しています。

でも、まだ途中なのでレジスタも6つ作って、さらに4bit化させる必要があります。

頑張ります。

NX RED VI制作を思い出す…

、、、これを作っている途中に、NX RED VIを作っているときのことを思い出しました。

「どんな暗闇も、道の途中」

これは、NX RED VIの調整をしていた時に聞いていた曲の歌詞の一部です。

そして、だんだん思ってきました。

「NX RED VIみたいなレッドストーンCPUを、もう一度作りたい」

、、、と

なので、考えておきたいと思います。

ですが、まずはこのGRED IIを作る方が先です。

完成!

というわけで、実行ユニットが完成しました!

、、、と言いたいところですが、まだレジスタの入力部分の回路や、I/O関係の回路が残っています。

加減算、インクリメント、デクリメントが行えます。

レジスタは6個です。

そして、今回はしっかり4bitです。

それでは、次回は実行ユニットの命令の入力部分と、I/O関係の回路を作っていきたいと思います。

今回は、約1時間半の作業でした。

お疲れさまでした。

それじゃあ、次回、また会いましょう