革命的だったのにお蔵入り!?ノイマン型レッドストーンCPU

前置き

みなさんは、ノイマン型アーキテクチャを聞いたことがありますか?

実は、このアーキテクチャを再現しようとしていたレッドストーンCPUがありました

ノイマン型とは

このアーキテクチャは、プログラムとデータを同じメモリに保存するアーキテクチャです。

ですが、このアーキテクチャは命令とデータを同じ配線で読み出すので、そこの帯域がボトルネックになってしまう問題がありました。

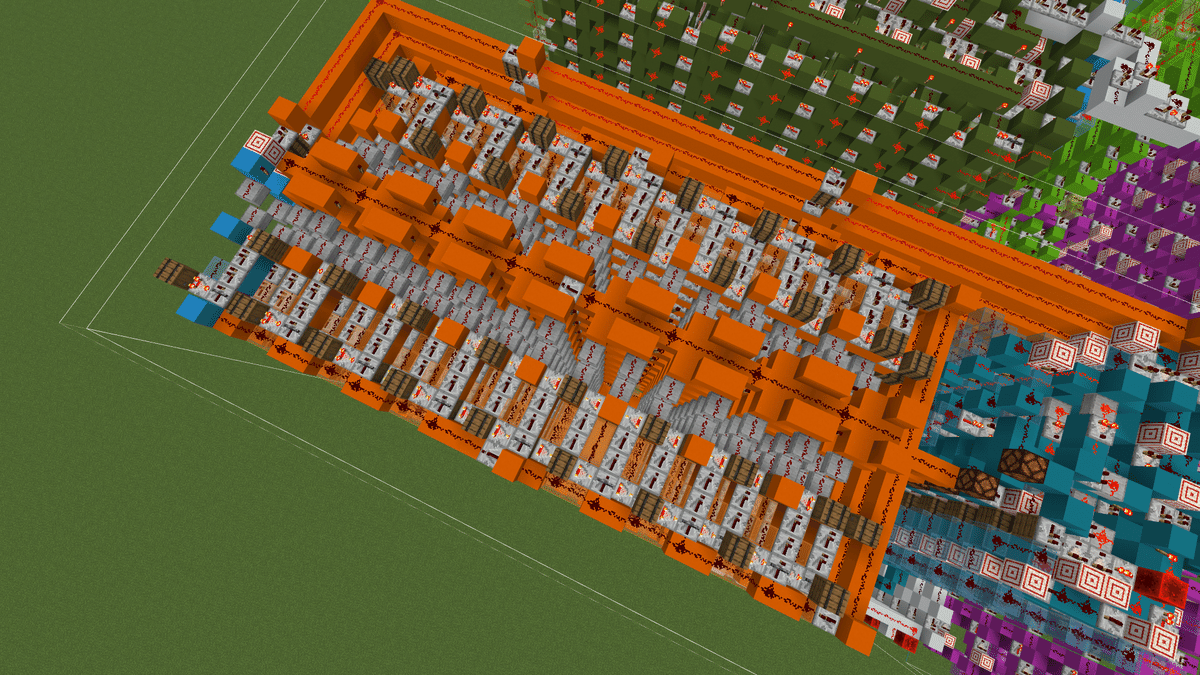

CRED XI(バージョン3)

ですが、僕のsushi memory architectureを活用することで、この問題を解決しながら、ノイマン型の汎用性の高さを活かせるようにしようとしたレッドストーンCPUがありました。

それが、CRED XI(バージョン3)です。

このレッドストーンCPUは、完成することはありませんでしたが、個人的に革命的だと感じたので、記事にしてみました。

なぜお蔵入りになったのかというと、サイズとスケジュールの問題があったからです。

サイズ面はかなりギリギリで余裕がなかったのに、まだ必要な回路が残っていました。

スケジュールとは、このCRED XI(バージョン3)を作っていた9月22日は、秋です。

SEASONシリーズのAKIを作る必要があるので、CRED XI(バージョン3)の優先順位は低く、お蔵入りになりました。

AKIが完成してからまた作ればいいと思った方もいらっしゃるかもしれませんが、実はしばらくするとCPUの詳細は忘れてしまうので、それは難しいんです、、、

ALU&レジスタ&I/Oポート

ALUは、加算、インクリメント、デクリメント、減算、XNOR、XOR、AND、OR、論理右シフト、右ローテートができます。

3rt CCAをベースにしていて、とても高速です。

レジスタは、合計で31Byteになっていて、汎用レジスタは30Byteです。

疑似16bit CPUなので、大量のレジスタが必要になっています。

プログラム側からは、15個のレジスタがあるように見えます。

PC(プログラムカウンタ)もセットになっていて、8bitです。

I/Oポートは、8ポートずつあって、信号強度式になっています。

特定のメモリアドレスと同期されていて、I/Oポートの情報にアクセスする場合はメモリにアクセスすることで、メモリを経由してアクセスできます。

メインメモリ&キャッシュメモリ

メインメモリは、512Byteの容量があって、メモリアドレスは8bitです。

ループ式のsushi memory architectureを採用しているので、サイズはすごくコンパクトになっています。

キャッシュメモリは、32Byteになっていて、実行ユニットの速度とメモリの速度から必要な容量を計算しています。

このキャッシュメモリは、命令専用ですが、このキャッシュメモリのおかげで、高速な演算が可能になっていたはずです。

スペック

ここに、詳細なスペックを載せておきます。

CRED XI(バージョン3)

スペック

8bit(疑似16bit)

クロック周波数:0.555~?(0.039以下)Hz

ALU:加減算、インクリメント、デクリメント、XNOR、XOR、AND、OR、論理右シフト、右ローテート

アキュムレータ:無し

汎用レジスタ:30Byte(疑似16bit×15)

I/Oポート:8ポートずつ

データキャッシュ:無し

メモリ:512Byte(16bit×256)

命令キャッシュ:32Byte(16bit×16)

ROM:無し

PC:8bit(実行ユニットに内臓)

回路サイズ:63×29×59(X×Y×Z)

高速化技術:クロック変動

日付:9月12日~9月22日

最後に

CRED XI(バージョン3)は、僕の中では初めて、ノイマン型レッドストーンCPUになる予定でした。

ですが、いろんな関係でお蔵入りになってしまいました。

ちなみに、バージョン1は没にした解説用CPUで、バージョン2はコンパクトなCPUもどきです。

バージョン2はそのうち記事にするかもしれません。

ノイマン型の経験は、HORSEや将来のSEASONシリーズで活かされる予定なので、いい経験をしたと思っています。

ちなみに、未完成品なので、配布はしません。

それでは、最後まで読んでいただき、ありがとうございました!