byte lane(バイトレーン)

複数の信号を同期させるパラレル伝送において、デジタル信号の1bit(ビット)をある情報の単位に束ねたものが1byte(バイト)である。

たとえばDDRメモリーでは、1bit x 8 = 1byteとなる。

基板設計において、高速パラレル伝送では特に等遅延で配線することが重要になる。1bitの論理値である0/1は、信号電圧のlow/highになる。また、配線1mmあたりの伝搬遅延は約6psである。複数の配線で遅延時間(≒配線長)を揃え、タイミングを合わせるということである。

DDRメモリーでは、DQS信号(データストローブ)とDQ信号(データ)の遅延時間を揃える。これをbyte lane(バイトレーン)と言う。laneとは車線のことで、基板では同じ引き回しにするという意味を持つ。

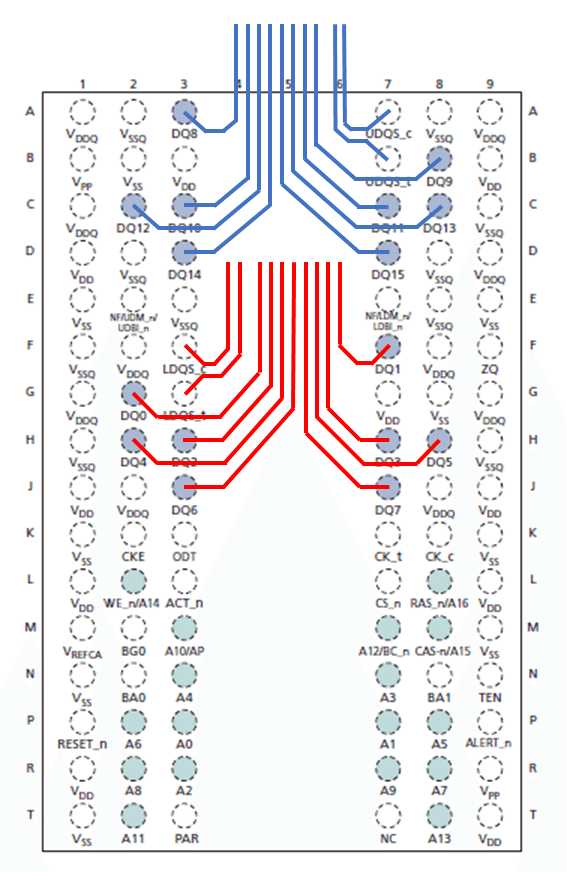

下図はあるDDR4メモリーのピンアサインである。

LDQS(差動)とDQ[0-7]、UDQS(差動)とDQ[8-15]がbyte laneの組み合わせになる。配線長を合わせやすいピンの位置になっていると分かる。

仮に配線を引き出すと次のようになる。各グループを別の層で配線することにより、部品の内側に引き出すことが可能となっている。

また、アドレス/コントロール信号を引き出すと次のようになる。メモリーを複数個並べた配置を想定しており、データ信号にクロスすることなく横方向に配線することが可能になっている。

引き出した後にミアンダと呼ばれる等長処理が必要になるが、引き出し方によって処理に必要なスペースや難易度が変わる。だからこそbyte laneの考え方や、複数ある配線層の使い分けが重要になる。