並列終端とプルアップの違いについて

並列終端とプルアップについて、LTSPICEを使用して抵抗の位置による波形の違いを確認しました。

並列終端……反射を無くし波形を整形する目的

プルアップ……無入力時に電圧をHighにする目的

違いをわかりやすくするため、どちらもVCC=1.2Vにしました。

また、並列終端はVCC/2(=0.6V)の終端にしていることに対し、プルアップはVCCとしています。

抵抗値について、並列終端は50Ω、プルアップは10kΩとしています。

線路モデルのTd=0.2nsは配線長40mm程度と同じです。

case1 並列終端

パルス電源を出力、5MΩをデジタルICの等価の入力抵抗に見立てます。

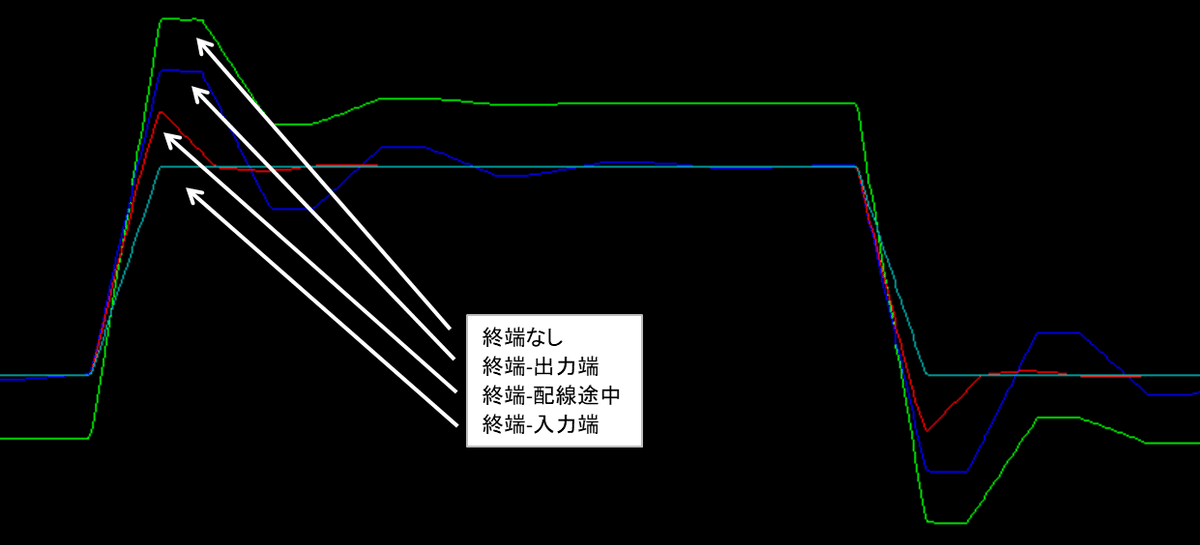

各入力抵抗の波形を重ね合わせると次のようになります。

並列終端は入力端に近いと良いことがわかります。

case2 プルアップ

各入力抵抗の波形を重ね合わせると次のようになります。

波形がどれもほぼ同じになります。つまり抵抗の位置はプルアップではどこでも良いとわかります。ではプルアップ抵抗は何のためにあるか。

出力端を開放(未接続)とした場合、10kΩと5MΩで1.2Vを分圧した値、1.197605Vで一定になります。

並列終端とプルアップは、どちらも抵抗を介して電源と接続します。

基板設計としては上記のとおり別であること、ご注意ください。

簡単ですが今回作成したデータを添付します。

(2023.3.31追記)

プルアップ抵抗の位置で波形を測定すると次のようになります。一見出力端に近い方がオーバーシュートが小さくなるように見えます。

これは反射の影響によるものです。

出力端では50Ω→5MΩの変化により、反射係数が1よりも大きい「正反射」が起きます。立ち上がりの段付きはこれによるものです。

入力端では50Ω→30Ωの変化により、今度は1よりも小さい「負反射」が起きます。これにより正反射で帰ってきた電圧(反射波)が小さくなります→結果的にオーバーシュートが小さくなったように見えます。

ただし、前述のとおりプルアップの位置によらず、入力端では波形は同じです。過渡特性は見るべきポイントをプローブすることが重要になります。