AMBA 5 CHI

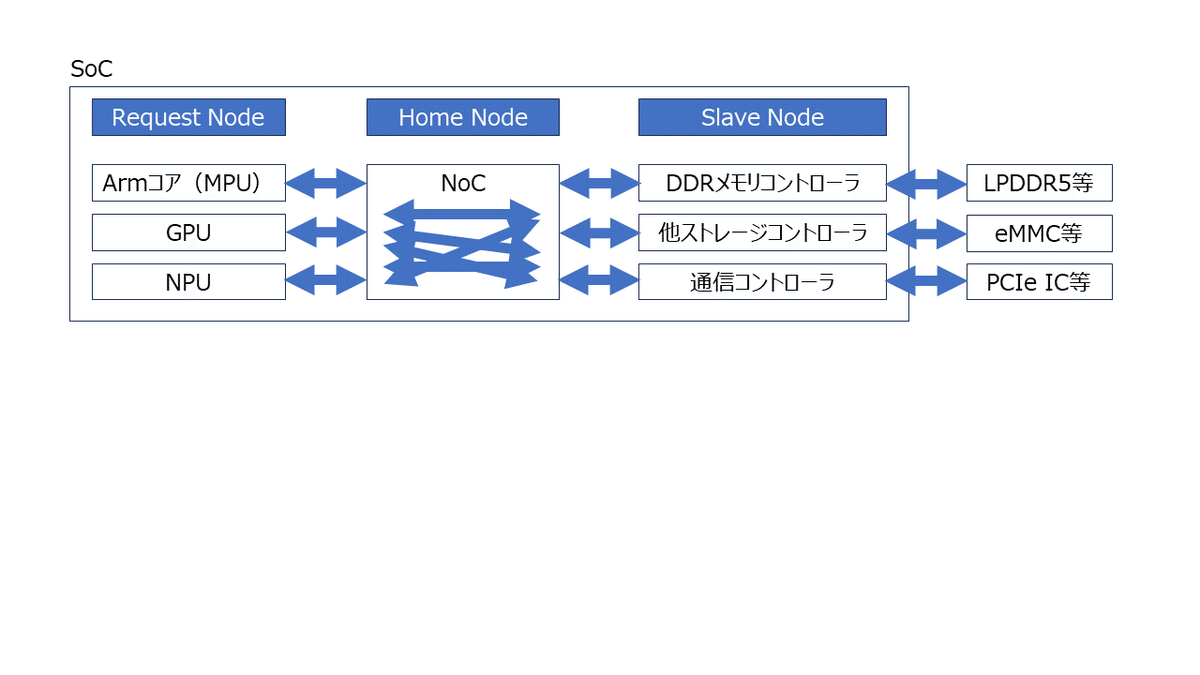

Armコアを採用してSoC(System on Chip)にする際の内部バスAMBA 5 CHIの概要を、メモリアクセスを中心に記載します。なお、AMBAは「Advanced Microcontroller Bus Architecture」、CHIは「Coherent Hub Interface」の略称になります。

AMBA 5 CHIとは

前VerのAMBA 4 AXI(Advanced eXtensible Interface)のインタフェースは、

・アドレス/データの相互接続をパイプライン化(注)

・データのやり取りは4KBまで

でしたが、AMBA 5 CHIのインタフェースは、大規模なArmコアをサポートするため、

・パケット/クレジットベースの通信

・データのやり取りは64Bまで

となっています。特に、CHIのポイントは、パケットを使った通信のようなNoC(Network on Chip)になります。

注…アドレスバス、データバス、制御信号(Validなど)で構成。パイプラインのように、リードリクエストを連続で発行し(ID付き)、コアへ送信されるリードデータの順序はアウトオブオーダで良い。アウトスタンディングトランザクションとも呼ばれる。

AMBA 5 CHIの特徴は以下の通り。

・req/ackによるデータやり取り(パケット/クレジットベース)。リトライやQoSを考慮したデータアクセスも可能。

・MPAM(Memory System Resource Partitioning and Monitoring)により、メモリ分離とそのモニタが可能。

・Slave Nodeがどのくらい処理状況なのかRequest Nodeに連絡。

・Request Nodeが、投機実行で処理しない予定のデータの読み出しを要望すれば、Slave Nodeは、LPDDR5等からデータをプリフェッチして、処理する/しないが確定するまでSlave Node内で処理しない予定のデータを保管(処理しなければ廃棄)。

・キャッシュのスヌーピングや、Atomic操作(下記、Atomic命令を参照下さい)なども含め、データのやり取りはHome Nodeで処理される。

・データのやり取り単位でArmのTrustZoneにも対応(暗号化されたセキュアモードでのアクセス)。

参考)Atomic命令

例えば、複数のスレッドが同じアドレスのデータを更新する場合、まず、スレッドAがデータを更新、その後、スレッドBがデータを更新ならば、問題は発生しない。ところが、スレッドAがデータ更新する前に、スレッドBがデータ更新を完了すると、「スレッドA更新後にスレッドB更新」が成立しておらず不整合が生じる。

そこで、ArmコアではLL/SC(Load-Link/Store-Conditional)という命令(LDXR/STXR等)をサポートしている。MIPSコアも同様の命令があると思います。LDXR/STXR命令は一対で実行されて意味を成します。まず、LDXR命令を使ってデータ更新を行いたいアドレスからデータをロードします。この時、該当するアドレスにはハード的にセマフォのフラグがセットされます。その後、STXR命令を使って該当するアドレスにデータを書き込む際、フラグがセットされていれば、予定通り該当するアドレスにデータを書き込み、更新完了となります(フラグはクリア)。もし、STXR命令で書き込む前に、他のスレッドが該当するアドレスにストア命令で書き込みを行ったら、STXR命令は実行されず、フラグは1にセットされます。

また、ArmコアのAtomic命令には、Compare and Swapという命令(CAS等)もあります。該当するアドレスのデータと指定された値を比較し、等しければ該当するアドレスに新たなデータを書き込みます。