UCIe(Universal Chiplet Interconnect Express)とは?:チップレット内部の共通接続規格💻

皆さん、スマートフォンやパソコンの中身について考えたことはありますか?これらのデバイスの頭脳とも言える半導体チップ。その世界で今、大きな変革が起きています。

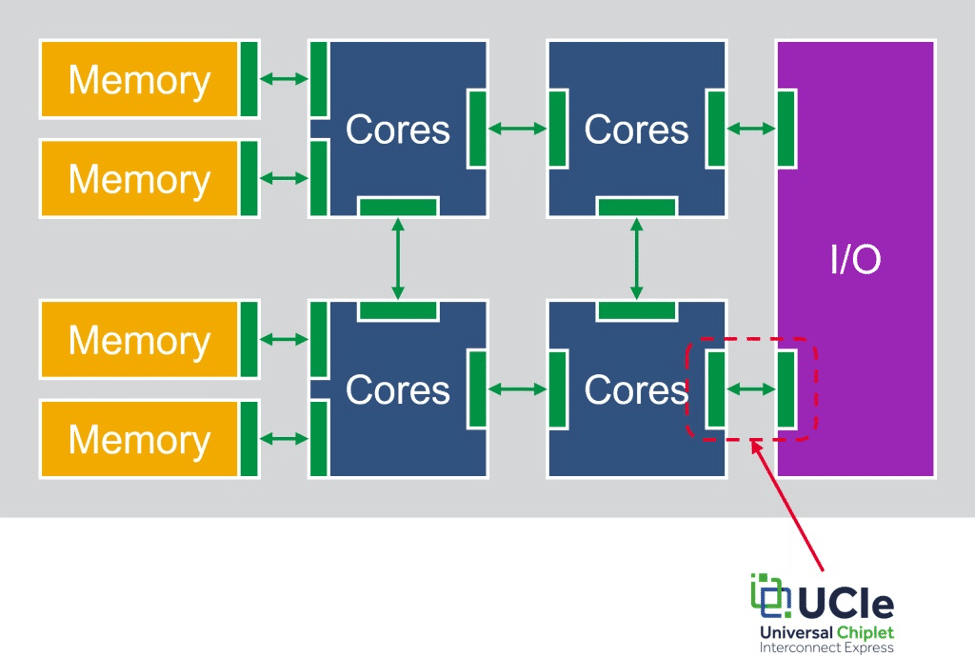

この記事では、その半導体チップを接続する規格である、UCIe(Universal Chiplet Interconnect Express)について、わかりやすく解説していきます。

(引用元:https://semiengineering.com/ucie-goes-back-to-the-drawing-board/)

Q: そもそも、UCIeって何ですか?

A: UCIeは、異なるメーカーが作った小さな半導体チップ(チップレット)を自由に組み合わせるためのインターコネクト規格です。これにより、より高性能で柔軟な電子機器の開発が可能になります。

チップレットとは、機能を分割した小さな半導体チップそのものを指します。製造プロセスの世代や機能が異なるチップレットを、ブロックのように組み合わせて1つのチップとして扱うことが出来ます。

チップレットの詳細については、こちらの記事で詳しく説明しているので、良ければ読んでみて下さい👇

チップレット技術の歴史と UCIe の誕生

半導体の歴史は、「小さく、速く、省電力に」という追求の歴史でした。しかし、物理的限界に直面し、新たな方向性として登場したのがチップレット技術です。

2000年代後半:AMDがマルチチップモジュール技術を開発

2010年代:IntelやTSMCなど大手企業がチップレット技術の研究を本格化

2022年3月:Intel主導でUCIeコンソーシアムが設立、UCIe 1.0仕様を発表

UCIeは、この長年の技術進化の集大成とも言えるのです。

UCIeの正確な定義とボードメンバーについては、HPに以下のように記載されています。

UCIe™ (Universal Chiplet Interconnect Express™) is an open specification that defines the interconnect between chiplets within a package, enabling an open chiplet ecosystem and ubiquitous interconnect at the package level.

Board members Alibaba, AMD, Arm, Advanced Semiconductor Engineering, Inc. (ASE), Google Cloud, Intel Corporation, Meta, Microsoft, NVIDIA, Qualcomm Incorporated, Samsung, and Taiwan Semiconductor Manufacturing Company along with our extensive Contributor and Promoter membership, are dedicated to this open industry standard organization and promoting and further development of the technology. Together we are establishing a robust global ecosystem to support chiplet design.

英語だと分かりにくいですね。日本語に訳すと、以下のような意味になります。

UCIe™(Universal Chiplet Interconnect Express™)は、パッケージ内のチップレット間の相互接続を定義するオープンな仕様であり、オープンなチップレットエコシステムとパッケージレベルでのユビキタス相互接続を可能にします。

ボードメンバーのAlibaba、AMD、Arm、Advanced Semiconductor Engineering, Inc (ASE)、Google Cloud、Intel Corporation、Meta、Microsoft、NVIDIA、Qualcomm Incorporated、Samsung、Taiwan Semiconductor Manufacturing Company、および広範なコントリビューターとプロモーターのメンバーは、このオープンな業界標準の組織と、この技術の促進とさらなる発展に尽力しています。私たちは共に、チップレット設計をサポートする強固なグローバル・エコシステムを確立していきます。

UCIeの一次情報を確認したい方は、こちらからご確認いただけます👇

UCIeの重要性:次世代半導体技術の鍵

UCIe(Universal Chiplet Interconnect Express)は、現代の電子機器開発において非常に重要な技術として注目を集めています。その重要性は、部品の組み合わせ自由度の向上、コスト削減、性能向上、そして省電力化という多面的な利点にあります。

UCIeの登場により、様々なメーカーの小さなチップ(チップレット)を自由に組み合わせることが可能になりました。

これは、例えばスマートフォンの内部構成を、異なるメーカーの最高の部品で作り上げることができるようになったことを意味します。

また、大きな1つのチップを製造するよりも、小さなチップを組み合わせる方が製造コストを抑えられるという経済的なメリットもあります。

UCIeの技術的特徴:革新的な二層構造

UCIeは大きく分けて3つの層から構成されています:

物理層:実際の電気信号やハードウェアの仕様を定義

ダイ間アダプタ層:チップレット間の直接的な通信を管理

プロトコル層:実際のデータ交換のルールを定義

これらの層が協調して働くことで、異なるベンダーのチップレットでも互いにスムーズに通信できる環境を実現しています。それぞれの層について詳しく見ていきましょう。

1. 物理層(Physical Layer)

物理層は、UCIeの基礎となる部分で、実際のハードウェアがどのように接続され、信号をやり取りするかを定めています。

この層の主な特徴は:

高速データ転送: 現在は1秒間に32ギガバイト以上のデータを送れる速さをサポートしています。将来はさらに高速化する予定です。

柔軟な接続: 必要に応じて、1本から16本までの「レーン」(データの通り道)を使えます。これは、高速道路の車線数を増減できるようなものです。

安定した信号: 電気信号の品質を保つための様々な工夦がされており、データを確実に送受信できるようになっています。

簡単に言えば、物理層はチップレット同士を「つなぐ」ための基本的なルールを決めているのです。

2. ダイ間アダプタ層(Die-to-Die Adaptor Layer)

ダイ間アダプタ層は、物理層の上に位置し、データの送受信を管理する役割を果たします。

主な機能は:

トラフィック制御: データの流れを適切に管理し、受信側が処理しきれないほどのデータが送られてくるのを防ぎます。

エラーチェック: データが正しく送られたかを確認し、間違いがあれば修正を要求します。

省エネ機能: 使っていない接続を一時的に休ませて、電力を節約します。

この層は、データのやり取りを円滑に、そして効率的に行うための「交通整理係」のような役割を果たしています。

3. プロトコル層(Protocol Layer)

プロトコル層は最上位に位置し、実際のデータ交換のルールを定めています。

主な特徴は:

互換性: 広く使われているPCIeという規格と互換性があるため、既存のシステムとも連携しやすくなっています。

柔軟なデータ処理: 大量のデータを扱えるようになっており、複雑な計算や処理にも対応できます。

優先順位付け: 緊急性の高いデータを優先的に処理する機能があります。

セキュリティ: 必要に応じて、データを暗号化して保護することもできます。

この層は、チップレット間で「何を」「どのように」やり取りするかというルールを決めているのです。

UCIeの進化:1.0から2.0へ

UCIeは時間とともに進化を続けており、バージョン1.0から2.0へと発展しています。UCIe 1.0では基本的な規格が確立され、最大32GT/sの通信速度と2mm以下のダイ間距離の最適化が実現されました。

続くUCIe 1.1では、セキュリティ機能の強化や、より柔軟なチップレットの組み合わせのサポート、消費電力の最適化機能が追加されました。

2024年8月6日にリリースされた最新のUCIe 2.0では、標準化されたシステムアーキテクチャのサポートにより、SIP(System-in-Package)における管理、試験、デバッグといった点での課題を改善しています。これによって、ベンダーに依存しないチップレットの相互運用が可能となります。

SiPは、複数のシリコンダイを一つのパッケージに収納し、システム全体を実現する技術です。SoC(System on Chip)と合わせて、こちらの記事で詳しく説明しているので、良ければ読んでみて下さい👇

また、UCIe2.0では新たに3Dパッケージングをサポートしています。従来の2Dや2.5Dパッケージングと比べて帯域幅の向上と電力効率の改善を実現しています。

加えて、ハイブリッドボンディングに最適化されたUCIe-3Dは、10~25μmと大きいものから、1μm以下と小さいものまで、幅広いバンプピッチに対応しています。

詳しくは、UCIeのHPに記載がありますので、チェックしてみて下さい👇

UCIeの未来:技術革新の原動力

UCIeは、スマートフォンやコンピュータ、自動運転車、AIシステムなど、私たちの身の回りのあらゆる電子機器の性能向上に貢献する可能性を秘めた重要な技術です。

その進化は、より高速で効率的、そして柔軟性の高い半導体技術の実現を目指して着実に進んでおり、今後の技術革新にも大きな影響を与えることが予想されます。

UCIeの発展は、単なる技術的進歩にとどまらず、電子機器の設計や製造プロセスの変革、さらには新たなビジネスモデルの創出にもつながる可能性があります。今後も、UCIeの動向に注目が集まることは間違いありません。

UCIe(Universal Chiplet Interconnect Express)のまとめ

UCIeは、半導体業界に革新をもたらす可能性を秘めた画期的な技術規格

異なるメーカーのチップレットを自由に組み合わせることが可能。設計の柔軟性向上、製造コストの削減、システム全体の性能向上、そして省電力化が実現。

物理層、ダイ間アダプタ層、プロトコル層の3層構造を採用し、高速通信と既存規格との互換性を両立。

UCIeは継続的に進化しており、バージョン1.0での基本規格の確立から、1.1でのセキュリティ強化や柔軟性の向上を経て、現在最新の2.0では、3Dパッケージ対応やハイブリッドボンディングといった次世代技術に対応。

UCIe規格は、スマートフォンから高性能コンピューター、自動運転車、AIシステム、データセンターに至るまで、幅広い分野で革新をもたらす可能性。

この記事が勉強になったよという方は、スキお待ちしています!

今後も、半導体やテクノロジーに関する分かりやすい記事をお届けしますので、見逃したくない方はフォローも忘れないでくださいね!

最後まで読んでいただき、ありがとうございました!

#UCIe #チップレット #半導体革命 #次世代テクノロジー #高性能コンピューティング

参考文献

おすすめ記事

いいなと思ったら応援しよう!