チップレットとは?:複数の小規模回路への分割⇒統合戦略💡

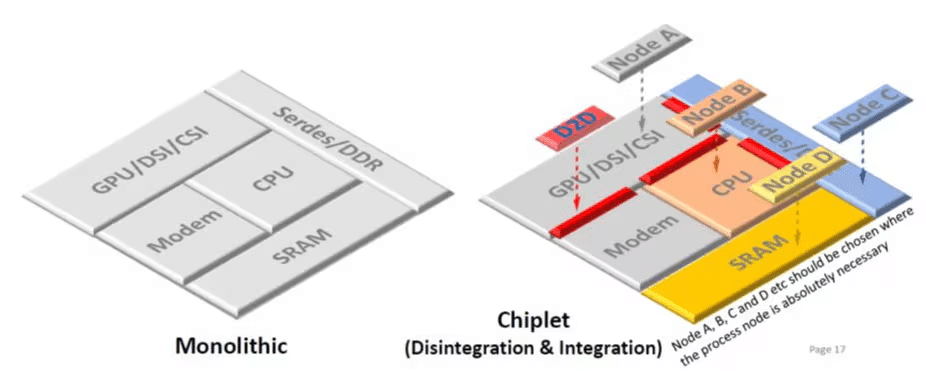

チップレットとは、従来の1つの大規模なチップに集積されていた回路を、複数の小さなチップに分割し、それらを組み合わせて1つの大きなチップのように機能させる技術です。

この記事では、チップレット技術誕生の背景やメリット・デメリットなどについて分かりやすく説明します✨

チップレットの概要

チップレットは、機能を分割した小さなチップそのものを指します。製造プロセスの世代や機能が異なるチップレットを、ブロックのように組み合わせて1つのチップとして扱えるようにする技術です。

出典:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1

具体的には、複数のチップレットを並べたり重ねたりして配置し、「インターポーザ」と呼ばれるチップレット間を接続する基板で相互接続することで、あたかも1つの大規模なSoC(System on Chip)のように機能させます。

チップレットの誕生背景

半導体は微細化を重ねて性能を向上させてきた歴史がありますが、チップレット技術の登場背景には、半導体の微細化の限界が見えてきたことがあります。

微細加工技術で作成されたチップは、製造過程で一定の確率で不良が発生します。この不良の発生は、製造条件のばらつきや、不純物・ゴミの混入が原因です。そして、チップ面積が大きいほど不良チップの発生頻度が高くなり、歩留まりが低下します。

これは、チップの一部に不良が発生すると、そのチップ全体が不良品と見なされるためです。当然歩留まりが低くなれば、その分製品単価に跳ね返りますので、価格競争力が低下します。つまり、半導体製品に関しては歩留まりを高めることは市場でシェアを取るために必須要件です。

チップ面積が大きな大規模回路を一括形成するよりも、回路を個片化して面積を小さくしたチップレットを寄せ集めた方が歩留まりは高くなります。個片化したチップレット1つひとつの歩留まりが向上するだけでなく、良品のチップレットだけを選別して大規模回路を形成できるからです。

実際の効果として、あるサーバー用チップの場合、全体を1つのチップで形成すると777㎟という巨大なチップになりますが、これを4つのチップレットに分けると、各チップレットの面積は213㎟になります。この場合、量産初期の歩留まりは1チップの場合はたった4%でしたが、チップレット化すると21%にまで向上します。この歩留まり向上効果は半導体の学会などの場で定量的に示されています。

出典:Greg Yeric, arm community,“Three Dimensions in 3DIC - Part I”, April 2, 2018

チップレットのメリット

1.異種統合が可能

処理能力が必要な部分は最先端プロセスで、入出力部分は信頼性の高い既存プロセスで製造するなど、用途に合わせて最適なプロセスを選択できます。

2.歩留まり向上

チップレットは小さな面積で製造されるため、製造欠陥の影響が小さく、ウェハーの歩留まりが向上します。

3.コスト削減

最先端プロセスを一部分にのみ使用すれば、コストを抑えられます。また、既存の古いプロセスを活用できるため、新規投資が少なくて済みます。

4.設計の自由度向上

機能ごとに最適なチップレットを組み合わせられるため、柔軟な設計が可能になります。新機能の追加や性能向上も容易です。

チップレットの課題

1.実装の複雑さ

チップレット間の配線が複雑になり、実装が難しくなります。電力消費や発熱、ノイズ対策など、新たな課題が生じます。

2.チップレット間の高速データ転送

チップレット間の高速大容量データ転送が必要不可欠です。インターポーザの性能が重要になります。

3.設計・検証の複雑さ

チップレットごとに設計・検証が必要で、全体の統合検証も求められるため、設計工程が複雑化します。

4.パッケージングコストの増加

チップレットを組み合わせるパッケージングコストが、従来のSoCよりも高くなる可能性があります。

チップレット技術の今後の展望

チップレット技術の今後の展望については、以下の点が考えられます。

異種統合の進展

チップレットでは、機能ごとに最適なプロセスやチップを組み合わせることができます。 この異種統合の自由度が高まり、より高性能で低コストな半導体の実現が期待できます。特に、メモリやRF(無線)、アナログ回路などの既存技術と、CPUやGPUなどの最先端ロジック回路を組み合わせた製品が増えると予想されます。

設計の複雑化への対応

チップレットでは、チップレット間の高速大容量データ転送が課題となります。 インターポーザの性能向上や、チップレット間の効率的な配線設計が重要になってくるでしょう。また、チップレットごとの設計・検証に加え、全体の統合検証が必要になるため、設計の複雑さが増します。 EDAツールの高度化や、設計自動化の進展が求められます。

パッケージングの発展

チップレットを組み合わせるパッケージング技術の発展が不可欠です。 FOWLPなどの先端パッケージング技術の普及が見込まれ、日本の材料メーカーや装置メーカーにとってビジネスチャンスになると期待されています。

新規参入の機会

チップレット技術により、半導体の設計や製造が従来よりも容易になる可能性があります。 そのため、新規参入企業が増え、半導体業界に新たな活力が生まれる可能性があります。一方で、チップレット間の接続技術や設計の難易度は高く、一部の大手企業への寡占化も危惧されています。 技術力の向上と標準化の進展が重要となるでしょう。

チップレット技術は半導体業界の新たな競争領域となり、日本企業にとっても追い風となる可能性があります。特に製造装置や材料分野で日本企業が貢献できる余地が大きいと期待されています。

参考文献

おすすめ記事

#半導体 #半導体関連 #半導体株 #半導体って何 #半導体の基礎

いいなと思ったら応援しよう!