A2PDP11 (11) プログラムの実行

RAM の読み書きができるようになりましたので、プログラムを実行してみます。

その前に、FPGA のコードを一部修正します。

top.sv

命令先読み時(AIO = 1100)にも、RAM を読むように変更。

読み出し命令が連続した時に、ram_read を正しく生成できるように変更。

バイト書き込み(ram_write)の時消しタイミングを修正。

parameter REQUEST_READ = 4'b1100; // Instruction-stream request read

always_ff@(posedge clk) begin

if (mbs == BS_MEM) begin

ram_addr <= mdal;

if ((maio[3:2] == 2'b10) || (maio == REQUEST_READ)) begin

miss_n <= (!ale_n && !bufctl_n) ? 1'b0 : 1'b1;

ram_read <= (!ale_n && !bufctl_n) ? 1'b1 : 1'b0;

mem_out <= ram_rdata;

dv <= !sctl_n;

end

end else begin

ram_read <= 1'b0;

mem_out <= 16'bz;

end

end

always_ff@(posedge clk) begin

if ((mbs == BS_MEM) && (maio[3:2] == 2'b00) && (!sctl_n)) begin

if (maio == BYTE_WRITE) begin

ram_byte <= 1'b1;

end

ram_write <= 1'b1;

ram_wdata <= dal[15:0];

end else begin

ram_write <= 1'b0;

ram_byte <= 1'b0;

end

endram.sv

バイト書き込み時のマスクの間違い修正。

data_mask0 <= {!ram_addr[0], ram_addr[0], 2'b11};ram_read の生成期間を短くしたので、読み出しデータ確定時に、rd1 の確認を省略。

always_ff@(posedge clk_out) begin

if (rd_data_valid0 && (rcycle == 1'b0)) begin

ram_rdata <= rd_data0[31:16];

end

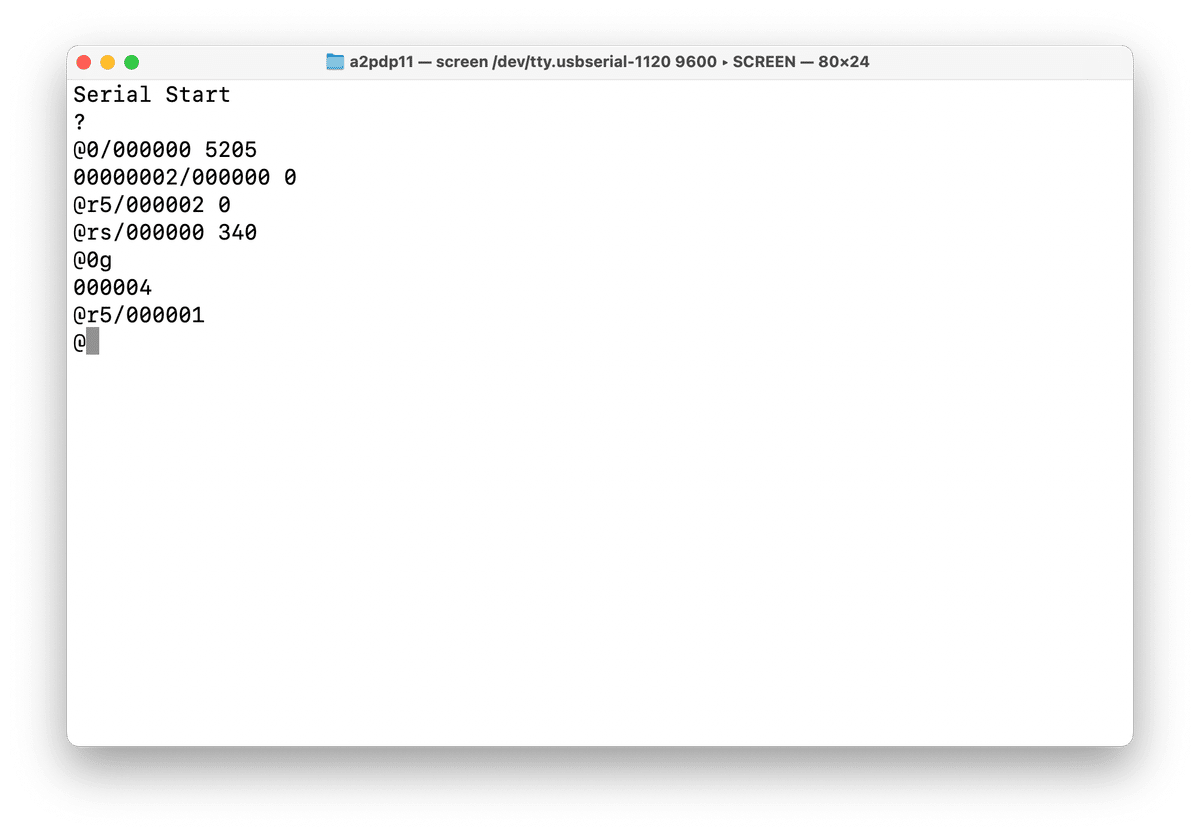

endPDP-11/HACK のテストプログラムを試してみます。

R5 をインクリメントし、HALT するプログラムです。

正常に動作しました。

実行時の信号を観察してみます。

黄色マーカー部で、アドレス 000000 の命令コード 005205(INC R5)が読み込まれます。

赤マーカー部で、アドレス 000002 の命令 000000(HALT)が先読みされます。

白マーカー部で、アドレス 000004 の命令が先読みされます。

オレンジマーカー部で、GP CODE 0 が発行されています。

参考文献

DCJ11 Microprocessor User's Guide, 1.5 HALTING DCJ11 OPERATION, 1983

PDP-11/HACK, Test Programs, 2014