特許分析:HBM(JP7349812,SKハイニックス)

特許番号:7349812

優先日:2018/11/30

登録日:2023/9/14

この発明は、高帯域幅メモリ(HBM; High Bandwidth Memory)を用いたメモリシステムに関するものです。特に、複数のメモリチップとチップ間でメモリを共有し、高効率なデータ伝送と低消費電力を実現するメモリシステムについて記述されています。以下に、発明の主要なポイントをまとめます。

発明の概要

高帯域幅メモリ(HBM)の利用:

本発明は、HBMを使用して高帯域幅と大容量のメモリシステムを構築することを目的としています。

複数のメモリチップの統合:

スマートフォンやタブレットPCの普及に伴い、データの生成速度や量が増加しているため、ビッグデータの処理に対応するために、複数のメモリを統合するプールメモリが求められています。

共有チャンネルによる効率化:

本発明は、メモリ内に共有チャンネルを設け、複数のチップがこの共有チャンネルを介してメモリを共有することができるメモリシステムを提供します。

これにより、データの伝送効率が向上し、伝送時に消耗される電力を減少させることができます。

実施形態

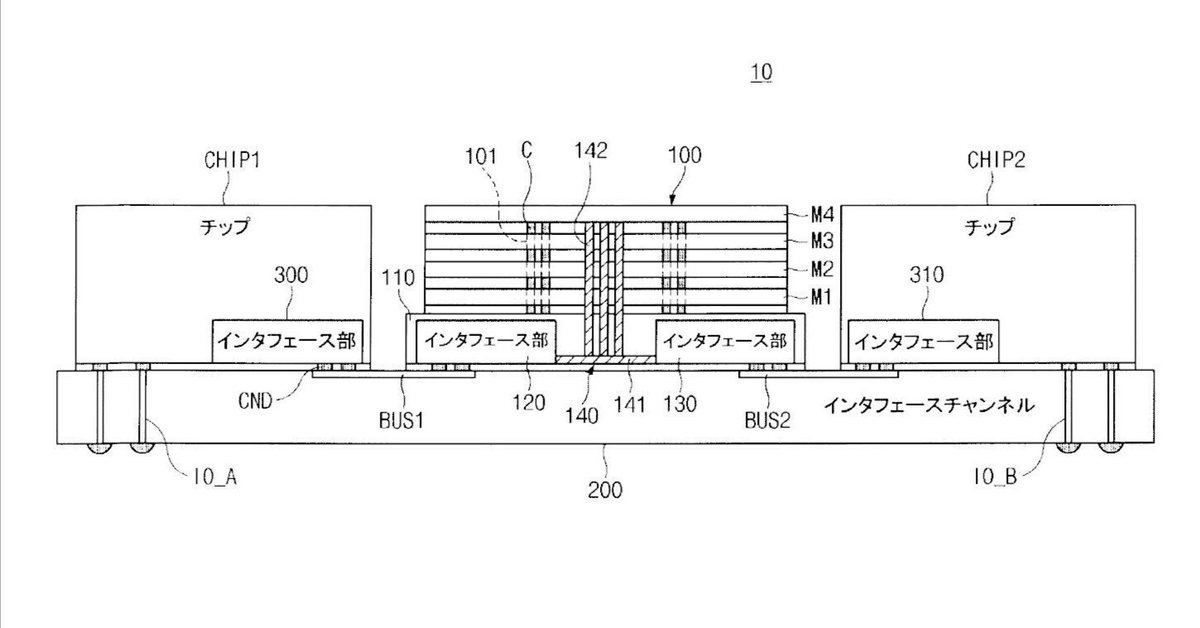

メモリシステムの構成:

メモリシステムは、第1動作を処理する第1チップと、第2動作を処理する第2チップ、およびこれらのチップ間で共有されるスタックメモリを含みます。

スタックメモリは複数のメモリダイを積層しており、貫通電極(TSV)を介して電気的に連結されています。

データ伝送の効率化:

共有チャンネル(共有バス)を介してデータを伝送することで、各チップはメモリ内で直接データを送受信できます。

制御部を設けることで、メモリコアとチップ間のアクセスタイミングを調整し、データの衝突を防ぎます。

多様なメモリの統合:

メモリシステムは、DRAM、PCRAM、ReRAM、フラッシュメモリなど、さまざまなタイプのメモリを統合できます。

複数のメモリは一つのパッケージ内で積層され、共有チャンネルを介して相互に連結されます。

システムインパッケージ(SIP)技術:

システムインパッケージ(SIP)技術を用いて、プロセッサダイとメモリダイをインタポーザインタコネクト技術を用いて一つのパッケージ内に統合することができます。

これにより、高速動作、大容量データ処理、多機能動作が可能となります。

効果

高いデータ伝送効率:

共有バスを介して直接データを伝送することで、データ伝送効率が向上します。

低消費電力:

データ伝送時の消耗電力を減少させることができます。

柔軟なメモリ配置:

異なるタイプのメモリを統合することで、システム全体の柔軟性と効率が向上します。

この発明は、特にビッグデータ処理や高性能コンピューティングにおいて、データの伝送効率と消費電力の最適化を図るための重要な技術として位置づけられます。

この発明における制御部の構成は、メモリシステム内でのデータ伝送効率を向上させ、消耗電力を減少させるために重要な役割を果たします。制御部の具体的な構成と機能について説明します。

制御部の具体的な構成

制御部の位置と役割:

制御部は、メモリコアと複数のチップ(CHIP1、CHIP2)との間に位置し、アクセスタイミングの調整を行います。

複数のチップ間でスタックメモリを共有する際に、データの衝突を防ぎ、効率的なデータ伝送を実現します。

ビジー信号(BUSY)の制御:

制御部は、メモリコアの動作状態を感知し、各チップにビジー信号(BUSY)を出力します。

ビジー信号が活性化されると、他のチップはメモリコアへのアクセスを待機状態にし、データの競合を避けます。

オアゲート(OR Gate)による信号処理:

制御部は、複数のオアゲート(OR1~OR4)を含み、これらのゲートはライト信号およびリード信号を処理します。

オアゲートは、ノード(NDA、NDB、NDC)に印加されるライト信号(NDA_WT、NDB_WT、NDC_WT)およびリード信号(NDA_RD、NDB_RD、NDC_RD)をオア演算し、ビジー信号(BUSY)を生成します。

制御部の詳細回路図

図4:制御部の詳細回路図

制御部は以下のように構成されています。

オアゲート(OR Gate):

OR1: ノードNDAに印加されるライト信号(NDA_WT)とリード信号(NDA_RD)をオア演算する。

OR2: ノードNDBに印加されるライト信号(NDB_WT)とリード信号(NDB_RD)をオア演算する。

OR3: ノードNDCに印加されるライト信号(NDC_WT)とリード信号(NDC_RD)をオア演算する。

OR4: OR1~OR3の出力をオア演算し、ビジー信号(BUSY)を生成する。

制御部の動作

ライトおよびリード信号の検出:

各ノードに印加されるライト信号またはリード信号が活性化されると、それに応じてオアゲートがビジー信号を生成します。

ビジー信号の活性化:

ビジー信号が活性化されると、他のチップはメモリコアへのアクセスを停止し、待機状態になります。

これにより、メモリコア内でのデータアクセスの競合を防ぎます。

アクセスタイミングの調整:

制御部はメモリコアの動作状態を監視し、ビジー信号を制御してチップ間のアクセスタイミングを調整します。

例えば、チップCHIP1がメモリコアにアクセスしている間は、チップCHIP2は待機し、アクセスが終了するとチップCHIP2がアクセスを開始します。

効果

データ伝送効率の向上:

制御部の働きにより、メモリコア内でのデータアクセスが効率化され、データ伝送の競合を防ぎます。

消耗電力の減少:

ビジー信号によって不要なアクセスを防ぐことで、消耗電力を減少させることができます。

高帯域幅の実現:

オアゲートとビジー信号を利用した制御により、複数のチップが効率的にスタックメモリを共有し、高帯域幅を実現します。

このように、制御部はメモリシステム内でのデータ伝送と消耗電力の管理において重要な役割を果たします。具体的な構成要素と動作メカニズムにより、効率的なデータアクセスと低消費電力を実現することができます。

この発明におけるメモリシステムでは、複数の種類のメモリが積層される可能性があります。以下に、具体的なメモリの種類についての記載をまとめます。

メモリの種類

本発明のスタックメモリに積層されるメモリの種類について、以下のような記載があります。

DRAM(Dynamic Random Access Memory):

これは最も一般的な揮発性メモリで、高速アクセスと大容量が特徴です。

PCRAM(Phase Change Random Access Memory):

フェーズチェンジメモリは、相変化材料を使用してデータを保存する不揮発性メモリです。高速な書き込みと優れた耐久性が特徴です。

ReRAM(Resistive Random Access Memory):

抵抗変化型メモリは、材料の抵抗値の変化を利用してデータを保存する不揮発性メモリです。高密度化が可能で、低消費電力が特徴です。

フラッシュメモリ(Flash Memory):

フラッシュメモリは、不揮発性メモリの一種で、データの電気的消去と再書き込みが可能です。NAND型とNOR型があり、ストレージ用途で広く使用されています。

記載の詳細

本文の該当部分を引用すると、次のようになります。

スタックメモリ100は、複数のメモリM1~M4が順次に積層されて多数のメモリM1~M2が統合されたパッケージ(Package)形態のメモリ装置であってもよい。それぞれのメモリM1~M4は、ディーラム(DRAM)、PCRAM(Phase Change Random Access Memory)、ReRAM(Resistive Random Access Memory)、フラッシュメモリ(Flash memory)など全ての種類のメモリのうち一つであってもよい。実施形態によって、多数のメモリM1~M4は同一のメモリ形態であってもよく、互いに異なるタイプのメモリであってもよい。

この記載から、スタックメモリに含まれる可能性のあるメモリの種類として、DRAM以外にもPCRAM、ReRAM、フラッシュメモリが考えられていることがわかります。

結論

本発明のメモリシステムにおいて積層されるメモリは、以下の種類を含む可能性があります:

DRAM

PCRAM

ReRAM

フラッシュメモリ

これらのメモリは、同一のメモリ形態で積層される場合もあれば、異なるタイプのメモリが組み合わされる場合もあります。これにより、システムの性能や特性に応じて最適なメモリ構成を実現することが可能です。