半導体チップ設計のTimeline(FablessとIDMの違い比較)

はじめに

今回は、IDMとFabless企業とで半導体チップ設計の時間的な違いを簡単に書いていきたいと思います。というのも自分はどちらも経験があるので、そのBackgrondを含め一般的な違いを分かりやすいようにまとめておきたいです。よく聞かれますし、忘れないようにとの意味合いもあります・・・。

もう少し上位概念から知りたい人は以前に書いたこちらの記事等をご参照していただけると幸いです。

自己紹介

日本の大学でPhDを取得し、日本の会社に就職するも会社の方針転換で一年も経たずに外部に出向し、先行きが見えないため別の日本企業に転職。なぜか転勤族になり西の方に移住。英語を勉強して外資系に転職しVISAをサポートしていただきUSに移住。その後GCを取得しBay Areaの大手テック企業に転職して今にいたります。専門は半導体のプロセス設計です。

転職に関する自己経験なのどは別のnoteにまとめていますのでご興味がありましたらご参照ください

IDM(自社Fabを持っていて設計・製造する)のTimeline

最初に自社Fabを持っている場合です。専用のFabが必要な場合は工場建設から装置選定および、導入した装置の立ち上げがあります。今回はこの部分は事前に実施済み、または既存の設備を流用して新規に製品を立ち上げるを前提とします。

工場立ち上げ等はかなり時間がかかるのでこの部分は、私の専門ではないので省かせていただきます。

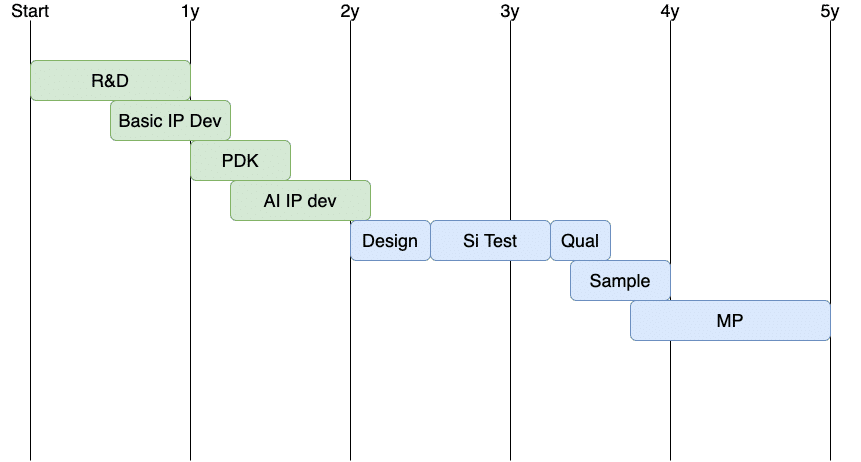

まずは大雑把なTimelineをみていきましょう。

自分の経験上でいうと基礎的なR&Dを開始して、製品用の開発および検証が終わり、製品出荷が始まるまでにおおよそ4年から5年かかるのが一般的かと思います。もちろん開発内容にもよりますが、新規技術採用の場合はこれぐらいが一般的だと思います。

IDMの場合はFab側とDesign側が一体となってIPやPDKを作ったりしたり、Si Testでマージンが少ないことがわかった場合にFab側で製造プロセスを最適化したりできるのが醍醐味です。

ここでは分かりやすいように階段状に区切ってはいますが、この限りではありません。Si Testぐらいまでは設計とFab側の協力関係が密に続きます。

FablessのTimeline

次にFablessの場合はどのようになるかをみていきましょう。結構違う点が色々とあります。緑がFoundry側で青がFabless側として書いてあります。

一番大きいところは、プロセスや基本的なIPお呼びPDKのことろは基本的にFoundry側が準備します。Designの一部で色がOverlapしているのは、場合によるからです。

共同開発などをする場合は、Fabless企業が開発する設計IPをどのように効率よく動かすかやDesign ruleをどうするかを協議する場合があります。これは結構稀なことで、よほどの大口顧客か力がないとできないかと思います。

一般的には、Foundryが提供するPDK以上のことはしてくれません。Fabless側は、そのPDK範囲内でDesignをするしかないです。

ここで重要なのは、Fabless側から見るとPDKが提供されるまでは自分のリソースは一切使っていないという点です。つまりFabless側から見ると、1.5yのところがStartになるのです。味方を変えると1.5y分時間とリソースを抑制できたとも言えます。この点は大きいですよね。

さらにいうと、MPに入ってからはFoundry側が責任を持って製造管理してくれますので、この部分のリソースを減らすこともできます。もちろん歩留まり管理の進捗やその他変動を早めにCatchするために何人かは引き続き見る必要がありますが、IDM程のリソースは不要です。

Rapidusの目指すところ

最近のものにも触れておきたいと思います。記者会見や一次情報を見ると、RapidusはこのようなTimelineを目指しているように見えます。

AI用のIPは事前に準備されており、それらを組み合わせてFabless側が自分のChipを設計する。少量短TATの最適化したラインでSi Testを短期間で終わらせる。という風に受け取っております。製造量や採算性は色々な方が議論しているのでさておき、技術者としてこれをみたときの感想と考察をまとめたいと思います。

Foundry側が提供するAI用IP

この部分はどのような内容のものかは全く情報がないのでわからないですが、考察すると、AIアクセラレーターになるのでは?と思っています。しかもLLMを処理するのに特化した非常に汎用的なものかと思います。というのもFablessが最も力を投入するところはIP設計です。なので、ある処理に特化したIPは絶対に自分たちで設計します。なので差異化の源泉にはならない汎用的な処理は提供されるIPを使うは可能性としてあります。

少量で短TAT生産

これは規模が小さい企業にとっては非常に助かるものです。強いて言えば乗合チップのシャトルサービスに対応してもっとVolumeが小さいものでも対応してくれると裾野は広がると思います。

まとめ

今回はIDMとFablessのTimelineの違いと特徴をまとめました。何かのご参考になればと思います。

いいなと思ったら応援しよう!