イメージセンサーBinningの勉強-1

はじめに

みなさんがお持ちのスマホ。これに必ずと言っていいほど実装されているカメラに関して自分なりに調べたものをメモがわりとして今回まとめておきたいと思います。ただカメラと言ってもカメラ自体ではなく、カメラに使用されているイメージセンサーに関してです。レンズやModuleに関しては全くの素人なので触れていません。また、個人の勉強のためにまとめているので引用等に関しては自己責任でお願いします。

Binningとは?

今回はBinningに関してまとめます。イメージセンサーに関してはかなり多くの資料や技術本が発行されているのでそちらをご参照されて方が良いかと思います。これらの資料や本等でほとんど触れられていない分野はBinningです。ですがこのBinningは非常に重要で、応用が広い機能です。なので、まとめておくのも良いかなぁと思い始めました。

ではBinningとは何かというと、こちらにありますように。イメージセンサーの信号をある塊にしてSN改善等を実施する方法です。こちらに書かれているものは非常に単純で基礎的なものなので、実際に使用されているものはかなり複雑です。また、現在主流となっているイメージセンサーはCMOS方式(CIS)なのでCCDとは考え方が大きく違うのでその点を考慮して書いていきます。

Binningの全体像

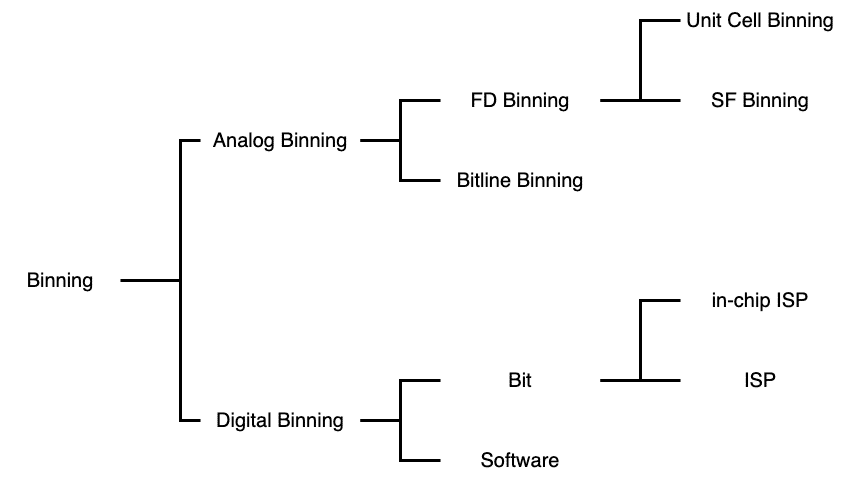

最初はどのようなBinning方法があるかをまとめておきます。それぞれに関しては何回かに分割してまとめていきます。

Binning方法は大きく分けてAnalog方式とDigital方式に区分できます。Analogはアナログ値を用いてBinningを実現する方法です。Digital方式はAnalog信号をDigital値にしてからBinningを実現する方法です。この点をごちゃ混ぜにしてしまうと、Noiseの計算やSN比の計算が間違ってしまいます。

Analog Binning

Analog Binningを理解するためには、実際にCISのPixel部分がどのように設計されているかをある程度理解しておく必要があります。なので最初に簡単なPixel構成を説明します。

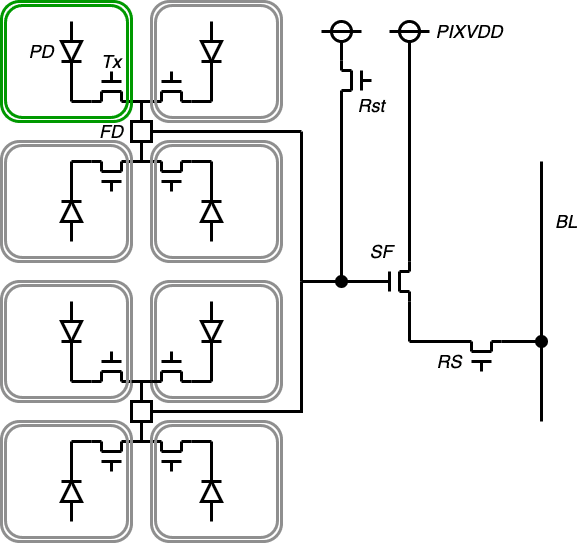

最近使われているCISは大抵複数のPixelが一つのFloating Diffusion(FD)を共有しています。この1つのFDを共有する単位をUnit Cellとしています。さらに、このUnit Cellが複数集まりSource Follower (SF), Reset (Rst)とRow Selector(RS)トランジスターを共有している場合もあります。文章では分かりづらいので簡単なLayut図を示します。例は4-pixelが1つのFDを共有し、Unit Cellを構成します。さらに2 Unit cellsがSF、RstとRSを共有する構成です。

回路図で書くとこのようになります。あくまで参考となるようにかなり簡略化したLayout図なので、実際にはDesign rule等を考慮してLayoutを最適化していきます。

FD-FDは配線で接続されており、この配線はRst Source/SF Gateにも接続されています。上下のUnit Cellの並列接続FD容量、配線容量及びSFのCgs容量の総量がこの2x4Unitの実行FD容量となります。

Unit Cell binningは、複数のPixel出力を共有しているFDに蓄積し、Binningを実現する方法です。これは非常にシンプルなのでイメージしやすいと思います。いくつのPixel出力をFDに蓄積させるかはPixel各々が有するTxを操作します。例えばUnit Cell内の2 Txを同時に開けると2 Pixelの出力がFDに蓄積され、2 pixelのBinningが実現できます。今回のLayout例では最大4 pixelまでが選択できます。

SF Binningは、Unit Cell Binningの応用です。Fig.3を参照すると、上4 pixelと下4 pixelのFDはSFのGateに接続されています。つまりSFのGateのところで上下 Unit CellのFD出力を加算することができます。このようにSFのGateでBinningする方法をSF Binningとします。回路の説明でも述べましたが、このSF Gateに繋がっているラインはそもそもFDの一部なので、分類としてはFD Binningとなります。

Bit line BinningはUnit Cell単位を超えてBL上でBinningを実現する方法です。かなり特殊な方法です。

Fig.4は参考回路図です。ここで緑色で囲まれたPixelの出力をBL上でBinningするとします。その場合、Pixelの出力はFDを介し、SF->RS->BLと信号が流れます。それが左右で行われるので、BL上でUnit Cellを越えたPixel出力をBinningすることができます。ここで気おつけてことは、BLにPixel出力を出すまでにSF/RSを介しているため、他のBinning方法よりもNoiseが大きくなります。この点がDemeritですがUnit Cellを越えたBinningができるので応用範囲が広がります。

Digital Binning

Digital BinningはBit演算またはSoftwareで実現するBinning方法です。CISはISPを内蔵しているためこのようなDigital Binningを内部で実装することが可能です。このCIS内部のISPでBit演算しBinningを実現する方法をin-chipとし、CIS内部のISPではなく、CISチップ外のISPでBinningを実現する方法があります。消費電力やシステム全体のコンセプトでどちらにするかを決めているようです。

Bit演算部分は読み出し方法と併せて説明したほうが良いので、次回以降に詳しく説明していきます。

まとめ

今回第一回目ということで、全体像に関してまとめました。次回からはもう少し細かくBinning方法をまとめます。

アメリカSilicon Valley在住のエンジニアです。日本企業から突然アメリカ企業に転職して気が付いた事や知って役に立った事を書いています。