コンピュータ・アーティテクチャの勉強note(編集中)

コンピュータの抽象化とテクノロジ

3つのタイプのコンピュータ

コンピュータの構成要素

入力

出力

記憶

データパス

制御

7つの主要なアイデア

設計を単純化するために抽象化する

一般的な場合を高速化する

並列処理を通じた性能の向上

パイプライン処理を通じた性能の向上

予想を通じた性能の向上

記憶階層

冗長性を通じた信頼性

プログラムの裏側

高級言語:CやJAVA,Pythonなどの一般的に認知されているプログラミング言語

コンパイラ:高級言語をアセンブリ言語に変換するシステム

アセンブリ言語:シンボル形式のプログラミング言語

アセンブラ:アセンブリ言語を機械語に翻訳するシステム

機械語:0と1で表記されるコンピューターへの指示

例:[a+b=c]をそれぞれでやってみる

高級言語: c = a + b

アセンブリ言語: add $t0, $s0, $s1 ($t0=c, $s0=a, $s1=b)

機械語: 000000 10000 10001 01000 00000 100000コンピュータの性能評価

CPU実行時間(該当プログラムにおける)

= クロック・サイクル数 × クロック・サイクル時間

= クロック・サイクル数 ÷ クロック周波数

= 実行命令数 × CPI ÷ クロック周波数

※CPI=命令当たりのクロック・サイクル数

MIPS (1秒当たりの命令実行数)

= 実行命令数 ÷ ( 実行時間×10^6 )

= クロック周波数 ÷ ( CPI × 10^6 )

命令:コンピュータの言葉

MIPS(アセンブリ言語)を使った命令

演算の対象となるデータ(オぺランド)はレジスタ(32本)に格納する

2^30のメモリは4刻みで値を保持する

MIPS → 機械語への翻訳

算術命令= op, rs, rt, rd, shamt, funct

例:add $t0, $s1, $s2

→ op(0), rs($s1), rt($s2), rd($t0), shamt(0), funct(add)

データ転送命令=op, rs, rt, constant(又はaddress)

例:lw $s1, 10($s2)

→ op(lw), rs($s2), rt($s1), address(10)

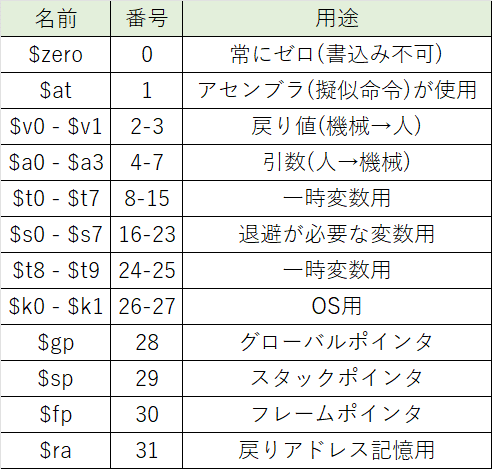

レジスタの割当

入れ子手続き

レジスタだけでは対応できないためスタックを使う。

スタックとは先入れ先出しの待ち行列であり、データの量はポインタ($sp)で管理する。

データの入力(push)はポインタを減算。

取り出し(pop)はポインタを加算する。

例:

int fact (int n)

{

if (n < 1) return (1);

else return (n * fact (n-1));

}

↓

fact:

addi $sp, $sp, -8 # スタックに2語文スペースを追加

sw $ra, 4 ($sp) # 戻りアドレスを退避

sw $a0, 0 ($sp) # 引数nを退避

slti $t0, $a0 ,1 # n<1 か否か

beq $t0, $zero ,L1 # n>=1 であれば、L1に分岐

addi $v0, $zero, 1 # 1を返す

addi $sp, $sp, 8 # スタックから2語文スペースを消す

jr $ra # 呼出し元に戻る

L1: # n>=1 の場合

addi $a0, $a0, -1 # 引数を(n-1)に設定

jal fact # factを呼び出す

lw $a0, 0($sp) # 引数nを復元する

lw $ra, 4($sp) # 戻りアドレスを復元する

addi $sp, $sp, 8 # スタックから2語文スペースを消す

mul $v0, $a0, $v0 # n*fact(n-1) を返す

jr $ra # 呼出し元に戻るプロセッサ

パイプライン処理(5ステップ)

命令フェッチ

命令デコード and レジスタ読み出し

命令操作の実行 or アドレス生成

データメモリ中のオペランドにアクセス

レジスタ書き込み

容量と速度の両立

キャッシュの性能測定

CPU時間=(CPU実行クロック数 + メモリ・ストール・クロック数)

× クロック・サイクル時間

メモリ・ストール・クロック数

=プログラム当たりのメモリ・アクセス件数×ミス率×ミス・ペナルティ

=プログラム当たりの命令件数 × 1命令当たりのミス件数

× ミス・ペナルティ

キャッシュミスへの対策

初期参照ミス:ブロックサイズを大きくし、プリフェッチを行う

容量性ミス:容量を大きくする

競合性ミス:連想度を大きくする

注意点

Verilog-HDLにおけるalwaysブロック内の組み合わせ論理

組み合わせ論理はすべて、1つの継続的代入文またはalwaysブロック内に置く

入力として使用する信号はすべて、必ずalwaysブロックのセンシティビティ・リストに含める

alwaysブロック内のどのパスでも、必ず同一のビット集合に対して値を代入する