FPGAなにそれおいしいの?から始める回路設計生活 | Campus OJT HWコースを受講してみて

enPITの最終課題でブログを書くらしいので,対抗してCOJTをやってみての感想を書きたいと思います。

Campus OJTとは

情報学群の3年生を対象とした、ソフトウェアとハードウェアの2つのコースがある授業です。

「組み込み技術キャンパスOJT」は、主に情報学群(情報科学類、情報メディア創成学類、知識情報・図書館学類)の3年次(過年度を含む)を対象とし、ソフトウェアとハードウェアの2つのコースに分かれて開講しています。インストラクターの講義や直接指導を行うとともにTAがサポートします。インストラクターは、それぞれの分野におけるエキスパートであり、受講生はその経験とスキルを十分に体験し、学習することができます。

コースがソフトとハードの2つがあり,私はハードなハードウェアコースを受講しました。

特徴としては,

ハードウェアコース

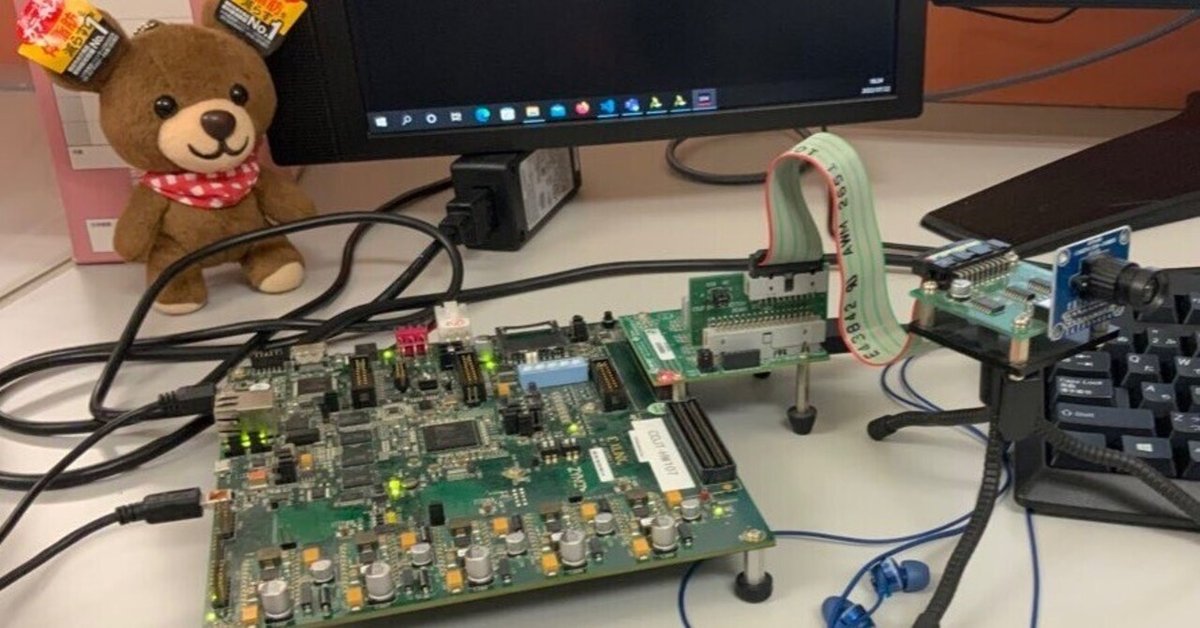

FPGAを使って映像入出力関係の回路設計をします。

FPGAとは、Field Programmable Gate Arrayの略で、プログラマブルなIC(Integrated Circuit)のことです。ユーザーがデザインした回路を実現することができます。FPGAは再配置可能なので、ソフト的に回路デザインの変更や修正が容易に行えます。

ソフトウェアコース

ネットワークやWebの機能を学びながら,何か面白いものを考えてものをつくるというかんじで楽しそうでした。隣の芝生は青かった時もありました。

成果発表会の様子を見るのが一番分かりやすいと思います。

FPGAなにそれおいしいの?から始める回路設計生活

初めは「FPGAなにそれおいしいの?」という気持ちから回路設計を学習することになりましたが、この場でいろいろな信号が並列で動いていくハードウェアの設計手法を学ぶことができました。1年間積み重ねたスキルはとても濃厚な経験になりました。おいしかったです。(タイトル回収)。

カリキュラム

春学期は仕様書や通信プロトコルを読み解いて実装をするというのがメインで,まずハードウェア設計に慣れようというものです。具体的にはモニターに画を表示させるための回路を設計します。

早く進んだ人はカメラ画像をFPGAに取り込む回路(秋学期の課題)を設計します。

その後,夏休みの課題なるものが出され,暇な人は取り組みます。

秋学期になると,仕様書が薄くなっていき,次第に自分でロジックを考えないといけなくなります。そうなると,変なロジックや回路を作ることになりかねないので,可読性や説明力が無いと,自分でちゃんと動作するように考えないといけなくなります。←自分でも分からなくなってくるので,ここがつらい

秋学期は画と画を重ね合われる描画回路や音を鳴らすサウンド回路を設計します。

そして成果発表会用に自作回路やアプリケーション開発をします。

実際どうやって開発していくのか?

ステップとしては,PC上でC言語の様にゴリゴリ書いていくVerilog HDLという言語でコードを書いていきます。if文とか,case文とか,フラグ管理などいろいろします。

そして,シミュレーターで波形を見ながらデバッグをします。意図した時に意図した信号が出ているかを確認していきます。

シミュレーションが上手くいき,回路合成(ワンクリックで可能)をして,問題なかったらFPGAに回路を流し込んでいきます。上手くいけば,動きます。

まあ,一発で正確に動作するってことはほぼなかったんですけどね。

ミスったら,どこにバグがあるか,波形を追って探すところから始まり,悪さをしている部分を改良し,またシミュレーター・実機でテストするというのを解決するまで繰り返します。

得たもの

そもそもCOJTがコンセプトとしている自分が将来勝負するレイヤーの上下を経験することで、やりたいこと・つくりたいものを実現する技術がみについたのではないかと思います。

作ったもの

私はBlicks Matching (レンガのパターンスキャナ)をつくりました。

4x4のレンガのパターンをスキャンし、そのパターンと情報を紐づけることができ、事前にそのパターンに情報を保存しておくと、後で誰かがそのレンガパターンをスキャンすると事前に保存した情報を読み出せます。

これを使えば、大学じゅうのレンガに情報を読み書きできるという、筑波大学をメディウムにした作品です。

Future WorksとしてARゴーグル化してしまえば、景観は汚さずにゴーグルを通して視界に情報を表示できるみたいなものも考えられます。

また、筑波大のレンガのパターンをNFT化かなんかをして売り出せば、3A棟2階の東側の面の(x, y)=(10, 10)番地のレンガという土地を売買するみたいなものになったら面白いんじゃなかろうかと思います。

まとめ

特にメディア創成では基本的に学ぶ機会がないハード寄りの授業なので、興味ある人にとっては良い経験になります

やる気と居残る時間があればなんとかなります

最近は対面授業が多く春日から本学まで大移動する場合もあるので,教室はPC環境がある上,24時間出入り自由な本学の拠点にできます(炊飯器を持ち込んではダメ)