DIGIC Acceleratorはとんでもない技術だぞって話

2024/7/17、延期に次ぐ延期で気を持たせられていた EOS R1、そして EOS R5 Mark II(以下、「R5II」と呼ぶ)が正式発表となりました。

事前の噂で盛られていたスペックの一部は実現されておらず、世間では他社機とのAF性能の違いはどんなものかな、程度の緩い反応……!?

ちょっと待って!

私は Youtube のプレゼンテーションをリアタイしていて、「Accelerated Capture」の模式図が出た瞬間に衝撃を受けました。

『センサーの真下に、DIGIC Accelerator がある……!?』

はい、この記事はキヤノンさんの新しい EOS R シリーズに搭載される DIGIC Accelerator が事前情報から想像していた以上のとんでもない技術だった、というお話です。

現状出ている情報からの推測に基くもので、信憑性には疑問符を付けておいてください。

また、キヤノンさんとは一切の関係はございません。

これはR5IIのメイン基板を左右反転したもので、チップは実物ではなくイメージのようです

以前より、DIGIC Accelerator の名称は噂になっており、AIの推論エンジンだろう、というのが世間の予想。

なので、DIGIC X の外付けチップとしてメインメモリを共有するNPUか、あるいはメモリ混載型の小規模な推論ユニットを DIGIC X に内蔵してしまうのだろうと考えていました。

しかし、Accelerated Capture というキーワードが出たことで、これ(DIGIC Accelerator)が単なる推論ユニットだけのものではないと気付かされます。

「Accelerated Capture」とは、すなわち、

『推論エンジンの能力を最大化するには、生データの一番近くに置け』

という設計思想です。

そう、私の想像していた方式だと、いったん(遅い)メインメモリに画像データを置いてから推論エンジンにかけることになるので効率が悪いのですね……。センサーからノータイムでデータを流し込むのが一番です。

ディープラーニングを活用したAF(つまり、AIの推論によるAF)は従来機の EOS R5 の DIGIC X 単体でも実現されていました(DIGICの持つ汎用DSPを推論エンジンに転用したか、あるいは既に推論ユニットが搭載されていたか)。

R5でシャッター半押しした状態で DIGIC X さんが何をやっているかというと、

センサーからの画像データ、位相差データをメインメモリに格納

画像データからEVF表示画像を生成、EVFに出力

各種センサー情報を元にISの制御

画像データを解析して露出のコントロール

画像データを解析してホワイトバランスのコントロール

画像データを推論エンジンにかけて、被写体認識

位相差データを元にフォーカスの制御

こんな感じで大忙しです。これらの処理は一定の周期で一定の作業量があるため、連写が始まると画像生成(とメモリカードへの保存)の処理はこの合間を縫って行うことになります。(初代 EOS R などは、DIGIC 8 のパワー不足により、このボトルネックによるレスポンス悪化が顕著でした。)

さて一方、DIGIC Accelerator が搭載された、R1、R5II では、Accelerated Capture により、センサーのデータは DIGIC Accelerator に直接流し込まれます。

そうすると、これまで DIGIC X さんが頑張っていた、1~2、4~7の処理は DIGIC Accelerator さんが行えば効率が格段に良くなります。

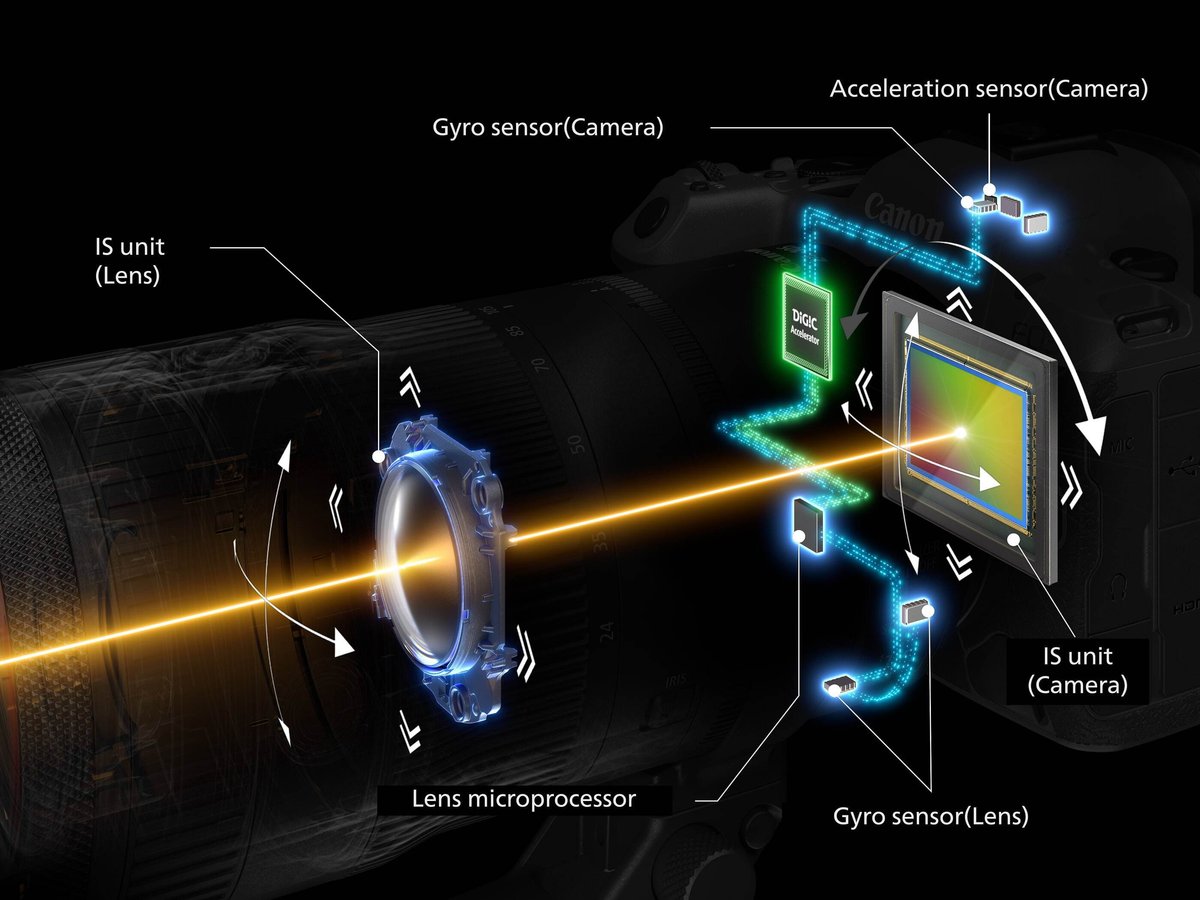

ちょっと待ってください。キヤノン公式サイト R5II の特徴紹介ページの手ブレ補正の項にある模式図を見てください。ISを制御しているのは……、DIGIC Accelerator です!

(https://www.usa.canon.com/shop/p/eos-r5-mark-ii)

ここの画像が日本のより大きかったので……

ということで、シャッターを押し切る前の処理は、全て DIGIC Accelerator で行い、余力のできた DIGIC X には画像処理に専念してもらえるようになります。DIGIC は進化の度にPCでの現像時にしか行えなかった処理をカメラ本体のみで実現したり、時間のかかっていた処理をリアルタイム化したりしてきましたが、さらに性能向上する余地が出来たということです。

(DIGIC X と DIGIC Accelerator が実際にどの程度、分業しているかは分かりませんが、IS制御までしているとなると、上記1~7の工程のほぼ全てを DIGIC Accelerator が実行する方が理に適っています。R5IIでデュアルピクセルRAWが利用できなくなったのも、位相差情報を DIGIC Accelerator のみで扱っているからと考えられます)

DIGIC Accelerator の内部構造を推察してみますと、まず、AIの推論ユニット、推論用のワークメモリ、DIGIC X との協調動作やEVF・ISを制御するためのスカラー演算ユニット、といったNPUに似た構成になるのではないかと思いますが……。

などと書きながら、デジカメWatchさんの実機テスト動画

( https://youtu.be/oNm_C5649ZQ?t=117 )

を見ていますと、R5IIのメイン基板と思われる画像が出てきました(1:57 あたりから)。

これまた衝撃です。

『えっ!? DIGIC Accelerator のチップサイズ……DIGIC X より大きい!? そして、メインメモリのチップが……無い!?』(※従来機では、メインメモリはDIGICの周囲に距離が均等になるよう配置されています)

推論エンジンの能力を発揮させるには、推論ユニットのなるべく近くに高速なメモリを配置するのが理想です。そして、画像データを現像のために DIGIC X に渡すオーバーヘッドはなるべく減らしたい……。もしかして、DIGIC Accelerator 、メインメモリ兼用の DRAM 混載型 NPU ではないでしょうか!?

もっとも、メインメモリは基板の裏側に実装されているのかもしれません。ただ、推論専用に設計されるユニットは低精度でもよく、小規模回路で低消費電力のものになるはずなので、あの大きなサイズはおかしい……。

考えれば考えるほど、デジカメ向けのアクセラレーターチップとしてはオーパーツのような存在に思えてきます。

実際、どんな構造なのでしょうね。

カタログスペック的には性能が少しずつ底上げされた正統進化、悪く言えばサプライズの無い機種という印象を持たれそうな R5II ですが、従来機からの性能向上、

AFトラッキング性能

AE細分化による測光制御

オートホワイトバランス精度の向上

手ブレ補正

ブラックアウトフリーファインダー

と、スペックアップしている箇所のほとんどが、DIGIC Accelerator の恩恵によるものです。おそらく従来機とは次元の違うものになるでしょう。その実力は、これから出てくる実機レビューで明らかになってくるはずです。

Accelerated Capture、DIGIC Accelerator の設計思想は、デジカメにおけるAI活用の理想形であり、ミラーレス移行から僅か数世代でここに辿り着いたキヤノンの慧眼・技術力に驚嘆するばかりです。

おしまい