Vivadoのクロック設定

FPGA では複数のクロックを使用するのが一般的になっています。

異なるクロック間の信号伝達は CDC(Clock Domain Crossing) と呼ばれ、メタステーブルが発生しないように正しく処理することが必要です。

CDC の処理方法については、ロジックの説明をしているページが沢山ありますので、ここでは触れません。ここでは CDC を処理したあと、ツールへの設定についての解説を行います。

非同期クロックによる信号は、ロジックで正しく処理する一方、FPGA の開発ツールでは、同一クロックで動作する信号が正常に伝達されることが必要です。

これは開発ツールで論理合成を行う際に判定されます。ロジックセルから次のロジックセルまでの伝達時間、クロックの遅延などを元に計算されるもので、開発ツールが自動的に判定します。

最終的に、論理合成結果には、クロック周波数は何MHzまで動作可能と記されます。

人が自分で調整出来るほど単純ではないので、開発ツールが自動でやってくれるのはありがたいことです。

その分、このクロックには何MHzの信号が入るのか、どのクロックとどのクロックは同期していて、どのクロックは非同期なのか、論理合成の前に設定が必要です。

設定にはいくつかの方法があります。今回は二つご紹介します。

一つはタイミング制約を行う xdc ファイルに直接テキストで入力する方法。

もう一つは Vivado の Edit Timing Constraints を使用してツール上で xdc ファイルの編集を行うことです。

1. xdcファイルの直接記入

これは指定するための書式や信号名が分かる時に行います。

テキストエディタを開いて xdc ファイルを編集すればいいだけですので、簡単です。

・クロック周波数の設定

FPGA に入力するクロック信号は周波数を指定します。例文は以下のようになります。

create_clock -period 20 -name clk_fpga_0 [get_pins {PS7_i/FCLKCLK[0]}]

create_clock というのがクロック信号であることを示します。

-period 20 はクロック信号の周期が 20ns、つまり50MHzであることを示します。

-name はクロック信号の名前を付けます。ここは自由に書いて構いませんが、分かり易い名前にしたほうが良いです。

最後の get_pins は入力ピンを示します。PS7_i/FCLKCLK[0] のピンに入力されているクロック信号の設定だということです。Zynqのクロック入力はこの名称でした。Zynqのような専用ピンではなく、ロジックに接続する信号の場合にはトップ層で指定した信号名になります。

周波数の設定には create_generated_clock という設定方法もあります。

これは MMCM や PLL など FPGA の内部で新しいクロックを作るときに使用します。IP の作成で MMCM を作った場合など、多くの場合ではユーザーが指定しなくても新しい周波数の設定がされますので、あまり使う機会はないと思います。

・非同期クロックの設定

複数のクロック信号や、クロック信号と非同期リセット信号のように、同期していない信号を指定します。これを指定しない場合には、Vivado は同期した信号だと判断するために、論理合成でタイミングエラーが大量に発生します。

set_false_path -from [get_clocks clk_fpga_0] -to [get_clocks clk_fpga_1]

非同期を示すのが set_false_path です。

その後、 from から to にむけての伝達ということで、それぞれの信号名を記入します。ここで信号名に入るのは、先の create_clock で name に記した名前です。

例文では clk_fpga0 から clk_fpga_1 への伝達は非同期であることを示します。これは一方的なものなので、逆方向、clk_fpga1 から clk_fpga_0 への伝達には適用されません。逆方向の信号伝達がある場合にはもう一行追加して set_false_path の指定をしなければいけません。

2. メニュー操作による非同期設定

こちらは書式がよく分からない。設定する信号はどんな名前で指定すればいいのか分からない、そういう場合に使用します。

先の例文で示した PS7_i/FCLKCLK[0] などは初めて Zynq を使った人には分からないと思います。

Synthesis を済ませないと実行出来ないこと、メニューから操作する分時間がかかることと、若干のデメリットはありますが、確実です。

方法は、①Run Synthesis を実行し、すぐ下の Open Synthesis Design を開けるようにします。②Edit Timing Constraints を実行すると、ウィンドウの右上にある Timing Constraints が開かれます。

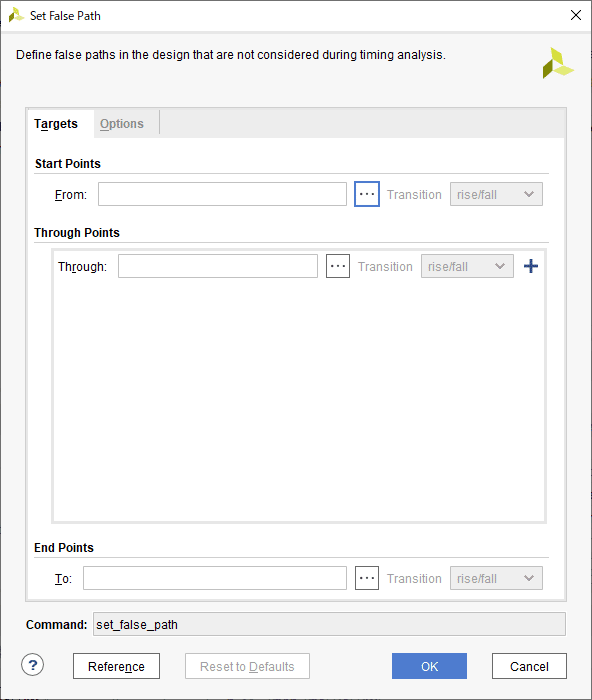

このスクリーンショットでは③Set False Path を示しています。これは非同期の設定です。同じように画面には出ていませんが Create Clock もあります。この③の部分をダブルクリックすると、信号の設定画面に移動します。

入力枠の右側にある「・・・」をクリックし、信号の選択ウィンドウから設定したい信号を選びます。

指定した結果、xdc ファイルに書き込まれるテキストは、ウィンドウ下部の Command に表示されるものと同じです。もし、xdc ファイルを勝手に変更されたくない、書き込む行を自分で選びたい、という場合には Commandの中身をコピーして貼り付けても構いません。

以上、二つの方法をご紹介しました。

Vivado には他にも Constraints Wizard を使用した設定方法や、Schematic から対象となる信号を引っ張ってくる方法などがあります。隠しコマンドかというくらい様々な方法がありますので、お時間のあるときにでも、いろんなコマンドを試してみてください。