FIFO Generator : Common Clock & Block RAM

FIFO Generator の記事の続きです。

前の記事では最初の Basic タブの説明だけで終わってしまいましたので、その続きで他のタブの設定内容について説明をしていきます。

Basicタブで何を選んだかによって、他のタブは内容も数も変わってきますので、今回は『Common Clock Block RAM』を選択した場合についてのみ記載します。それだけでも長いので。

1.Native Ports

Read Mode

Standard FIFO と First Word Fall Through の二択です。

ここで何が変わるのかというと、FIFOに入力された始めの1word目が出力にどのタイミングで反映されるかの選択となります。

基本的には、FIFOに入力されたデータはRead信号を入力することで出力信号に反映されます。こちらがStandard FIFOです。

一方 First Word Fall Through を選択した場合には、FIFOに入力された時点で出力信号に反映され、Read信号を入力すると2word目のデータが出力されるようになります。

出力信号とRead信号の数が一つずれると思って下さい。

Data Port Parameters

入出力のデータ幅、FIFOの深さの設定を行います。

Write Width が入力データ幅の設定で、Write Depth が FIFO の深さです。

出力のデータ幅は Read Width です。こちらは Write Width で決めたデータ幅と同じか、半分、2倍、4倍、8倍という感じで入力データ幅を基準に選択式になります。

同様に、 Read Depth は自動で決まります。入出力ポートのデータ幅が等しければ Write Depth と同じ値に、半分の幅であれば倍の深さに設定されます。

ECC, Output Register and Power Gating Options

ECC の設定と出力レジスタの有無、パワーゲーティングと呼ばれるスリープモードの設定を行います。パワーゲーティングは UltraScale デバイスで使用可能な機能ですので、今回、説明に使用しているプロジェクトでは使うことが出来ません。

ECC のチェックボックスにチェックを入れると ECC が有効になります。

ECC 有効時のみ Single Bit Error Injection、Double Bit Error Injection が使用可能です。この2つはテスト用の機能で、故意にエラーを発生させることが出来ます。

ECC Pipeline Reg は ECC パイプラインのレジスタを有効にするもので、有効時には1クロックの遅れが発生します。これを有効にすることによって、配線遅延をレジスタで切ることが出来ますので、最終的な動作クロックを向上させることが可能です。この機能は Built-in FIFO ブロックを使った時だけ設定可能です。今回は Basic で Block RAM を選択しているため、使用出来ません。

Dynamic Power Gating はスリープモードを言ったほうが分かり易いと思います。スリープ中は FIFO を動作させることは出来ませんが、消費電力を少なくすることが出来ます。この機能を使用出来るのは UltraScale デバイスだけです。

Output Registers は出力ポートにレジスタを挿入するものです。この機能を有効にすることで1クロックの遅れが発生します。これを有効にすることによって、配線遅延をレジスタで切ることが出来ますので、最終的な動作クロックを向上させることが可能です。

個人的な経験で言うと、Output Registers は入れたほうが良いです。入れないと出力遅延が大きくなりすぎて、クロック周波数が高く出来なかったり、レポート上は間に合ってるはずなのにデータ化けが発生したりと、トラブルになりがちです。

挿入するレジスタは Embedded Registers と Fabric Registers から選択出来ます。これは挿入するレジスタをFPGAのどこの部分で使うかという選択です。ここは特に変更せずに Embedded Registers で良いと思いますが、もし、どうしてもタイミングが間に合わないのであれば、変更してみるのも手です。

Initialization

最後は初期化の設定です。リセットピンの使用と、同期リセットか非同期リセットか。リセット時のフルフラグの出力、リセット時の出力データの値を設定します。

2.Status Flags

Optional Flags

オプションのフラグを使うかどうかの設定です。

増やせるオプションフラグは2つ。Almost Full Flag は、後1ワード書き込んだらFIFOが一杯になることを示します。Almost Empty Flag は、後1ワード読み込んだら FIFO が空っぽになることを示します。

書き込み制御や、読み込み制御でフラグを見て瞬時に反応出来るのであれば必要ありませんが、反応するために1クロック、時間が必要な場合には有用なフラグです。

Handshaking Options

こちらもオプションの信号です。

Write Acknowledge は書き込み応答、 Overflow はFIFOの深さを超えた書き込みの発生。 Valid Flag は有効データ、 Underflow Flag は FIFO が空っぽなのにリード要求を出してしまったときにアクティブとなります。

それぞれ、発生時に H を出力するか、 L を出力するかが選択出来ます。

Programmable Flags

FIFO が一杯であることを示す Full Flag と 空っぽであることを示す Empty Flag のオプションです。

ここを変更することで、完全に Full にならなくても一定量のデータが入力されたときに Full Flag を立てたり、完全に空っぽでなくても Empty Flag を立てたりすることが出来ます。

例えば、入力データが 16word セットになっていて、読みだす時も 16word 溜まってから読み出したい、という場合に使用します。

ここを良く見ると分かるのですが、デフォルト設定では FIFO の深さを1024に設定した場合でも、Full Flag が立つのは 1022word 溜まった時になります。

これ以上増やすことは出来ません。つまり 1024 の深さがあっても、 1024word 保存することは出来ないということです。ご注意下さい。

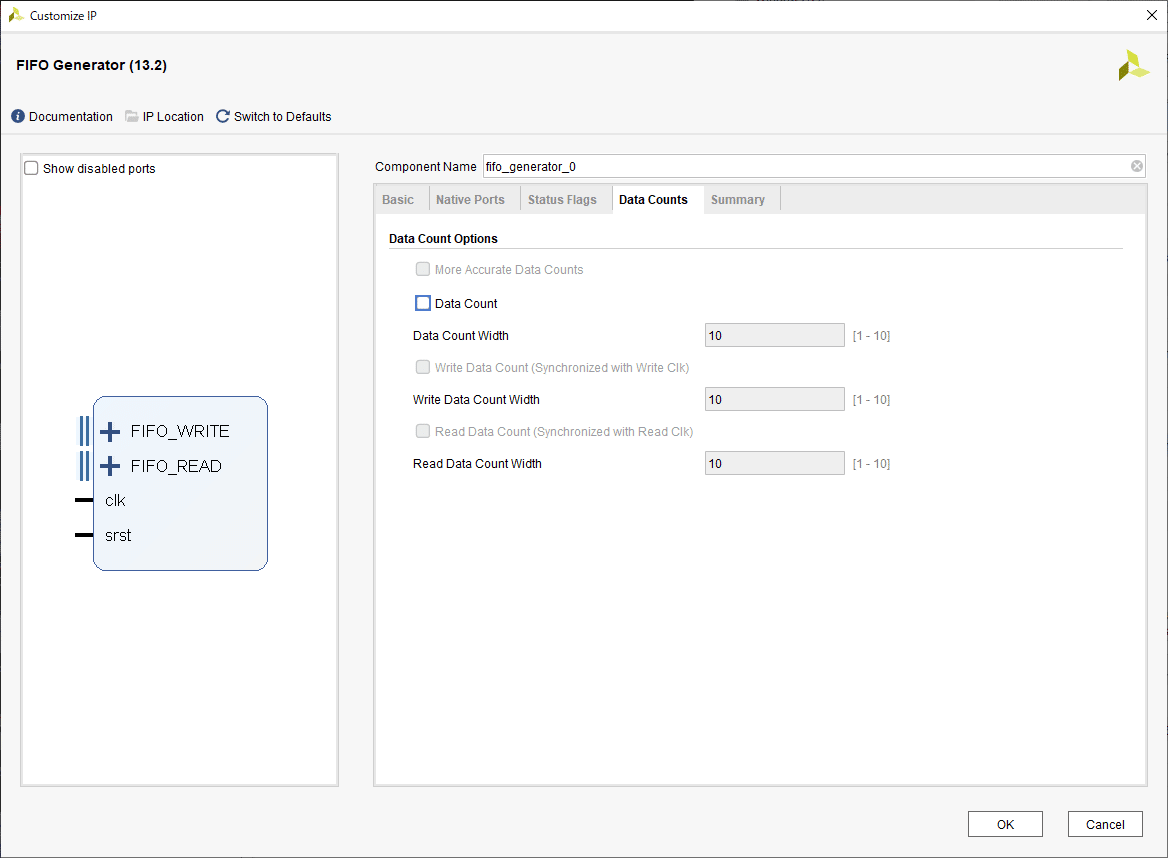

3.Data Counts

Data Count Options

一つ前の Status Flag のタブでは Full や Empty のフラグの設定をしました。ここではもっと直接的にデータ量をカウントして出力してくれます。

入力側、出力側、それぞれでカウント値を出力してくれます。

今回の構成では、入出力のクロックは同一ですので、どちらでも良いと思われがちですが、入力側と出力側ではカウント数の反映が数クロックずれますので、正しい方向のカウント値を使って下さい。

入力側のカウント値で出力側の読み出し制御を行うと、まだ、データが出力側に届いておらず、データが読みだせない場合があります。

4.Summary

最後の Summary は書いてある通り、結果の表示です。変更する項目はありません。

今までのタブで設定してきた結果が表示されますので、設定洩れや、設定ミスがないか確認して下さい。

また、一番上に表示されている Block RAM resource も確認して置くと良いでしょう。

ここには設定の結果、FPGA 内の Block RAM を幾つ使ったのかが表示されます。Block RAM の数は有限ですので、無駄に使ってないか確認しておくクセをつけると、後々、幸せになれます。理由を説明します。

Block RAM は 1ブロック 36Kbit で構成されています。これを分割して18Kbit x 2 の2つに分けて使用することも可能です。

このとき、Block RAM にも深さの制限、データ幅の制限があります。

8bit x 4096 は1つの Block RAM で構成出来ますが、 128bit x 256 は同じ容量であっても2つの Block RAM を使用します。データ幅が大きいからです。これを理解していないと、見積もり上は入るはずだったのに、実際には Block RAM が足りなくなってしまうという事態になります。

ここまでで全てのタブの設定を説明しました。

細かい説明で足りない所もあるかと思いますが、使うために押さえておいたほうが良い内容は以上となります。

設定が終わったら OK ボタンを押すと IP が生成されます。生成された後では IP をダブルクリックすれば、もう一度、構成を変更することも可能です。あまり心配せずに OK を押してみて下さい。