JPEGエンコーダー・デコーダのロジック回路を設計してみる①(DSLX編)

背景

ここ1年、資格を取ったり、半年前からNoteに好き放題に半日程度で設計できる初歩的なロジック回路の設計をUpしてきた。ここまでは1年半前に奥さんに話した計画通り。3月にGPUの成果物をUpするのも計画通り。

最後に学生の時に設計してみたかったJPEGエンコーダー・デコーダー回路を設計してみよう。

(来年度のやりたいこと・やることは、ちゃんと計画しています。ロジック設計ではありません。)

一旦はロジック設計関連は最後と言うことです。

JPEGとは?

JPEG: 画像圧縮のアルゴリズムですよね。

理論は下記

参考サイト

Pythonで書いたアルゴリズムは下記サイトから。

JPEGエンコーダー

JPEGデコーダー

JPEGのアルゴリズムとは?

wikiなどを読めば分かるように

RGB-YCbCr変換

DCT変換

量子化

ジグザグスキャン

ハフマン圧縮

の順番で実行していきます。最後にバイナリにヘッダーを付ける。

ロジックを設計する方針を考える

Githubを見ながら考えてます

ざっと調べたところ、今は情報が豊富な時代です。

DCT変換は固定係数、量子化の段階で圧縮率を決める。

8x8ピクセルのエンコーダなら2時間あれば作れるかな?

以下作業中

DSLXコード

RGB-YCbCr変換

file: rgb_ycbcr.x

完成済み。

// NISHIHARU

// Converts an RGB pixel value into YCbCr format.

fn rgb_to_ycbcr(r: u8, g: u8, b: u8) -> (u8, u8, u8) {

// Convert r, g, b to 16-bit signed integers for calculation.

let r_16bit = (u8:0 ++ r) as s16;

let g_16bit = (u8:0 ++ g) as s16;

let b_16bit = (u8:0 ++ b) as s16;

let y_16 = (s16:77 * r_16bit + s16:150 * g_16bit + s16:29 * b_16bit) >> 8;

let y = y_16 as u8;

let cb_16 = (s16:-43 * r_16bit + s16:-85 * g_16bit + s16:128 * b_16bit) >> 8;

let cb = cb_16 as u8;

let cb = cb + u8:128;

let cr_16 = (s16:128 * r_16bit + s16:-107 * g_16bit + s16:-21 * b_16bit) >> 8;

let cr = cr_16 as u8;

let cr = cr + u8:128;

// Output Y, Cb, Cr values for debugging purposes.

trace!(y);

trace!(cb);

trace!(cr);

// Return the converted YCbCr values.

(y, cb, cr)

}

結果

→OK

1次元DCT変換

file: DCT_1D.x

完成済み。結果→test OK

2次元DCT変換

file: DCT_2D.x

完成済み。結果→test OK

→16CLK以上の

DCT_2D_proc.x に変更するべき

量子化

file: JPEG_quantize.x

完成済み。結果→test OK

ジグザグスキャン

file: Zigzag_scan.x

完成済み。結果→test OK

→ここもZigzag_scan_proc.xへ変換すべき

ハフマン圧縮(DC)

file: Huffman_DCenc.x

完成済み。結果→test OK

ハフマン圧縮(AC)

file: Huffman_ACenc.x

完成済み。結果→test OK

全体を組み上げてみる

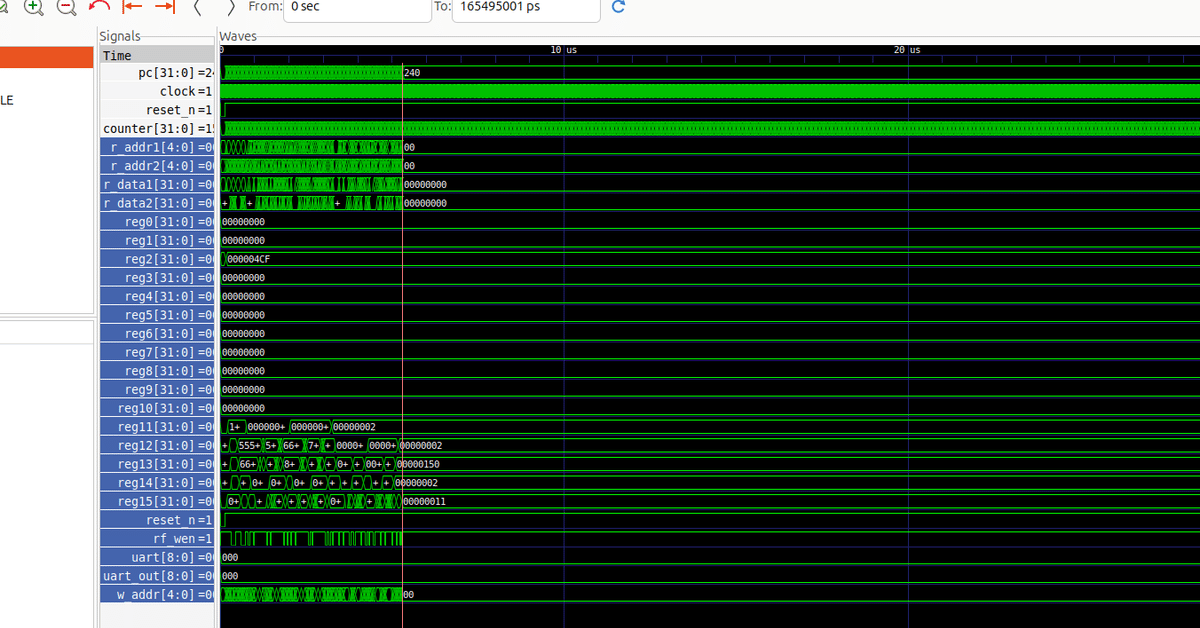

JPEGエンコーダー・デコーダのロジック回路を設計してみる②【Verilog設計】

に続く。

所感

JPEGエンコーダーのDSLXコードを設計しました。

DSLX→Verilogに変換する。

全体を組み上げるにはVerilogで設計します。